# SmartFusion2 SoC FPGA Code Shadowing from SPI Flash to DDR Memory - Libero SoC v11.7

DG0386 Demo Guide

Power Matters."

# Contents

| 1 | Prefac<br>1.1<br>1.2<br>1.3     | Ce       5         Purpose       5         Intended Audience       5         References       5                                                                                                                                                                                                                                                                                | 5                               |

|---|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 2 | Smart<br>2.1<br>2.2<br>2.3      | Fusion2 SoC FPGA - Code Shadowing from SPI Flash to DDR Memory       6         Introduction       7         Demo Design       7         2.3.1       Introduction       7         2.3.2       Description       7         2.3.3       Creating Target Application Image for DDR Memory       12         2.3.4       SPI Flash Loader       13         Running the Demo       13 | 6777823                         |

|   | 2.5                             | Setting Up the Demo Design       13         2.5.1       SPI Flash Loader and Code Shadowing Demo GUI       14         2.5.2       Running the Demo Design for Multi-Stage Boot Process Method       15         2.5.3       Running the Hardware Boot Engine Method Design       19         Conclusion       21                                                                 | 3459                            |

| 3 | Apper                           | ndix: DDR3 Configurations                                                                                                                                                                                                                                                                                                                                                      | )                               |

| 4 | Apper                           | ndix: Generating Executable Bin File                                                                                                                                                                                                                                                                                                                                           | ;                               |

| 5 | Revisi                          | on History                                                                                                                                                                                                                                                                                                                                                                     | 5                               |

| 6 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5 | ct Support27Customer Service27Customer Technical Support Center27Technical Support27Website27Contacting the Customer Technical Support Center276.5.1Email27276.5.2My Cases6.5.3Outside the U.S.Caster Support28                                                                                                                                                                | 7<br>7<br>7<br>7<br>7<br>7<br>3 |

|   | 6.6                             | ITAR Technical Support                                                                                                                                                                                                                                                                                                                                                         | 5                               |

# **Figures**

| Top-Level Block Diagram                                      | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Code Shadowing – Multi Stage Boot Process Demo Block Diagram | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Design Flow for Multi-Stage Boot Process Method              | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Code Shadowing – Hardware Boot Engine Demo Block Diagram     | . 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Top-Level Block Diagram                                      | . 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Design Flow for Hardware Boot Engine Method                  | . 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| USB to UART Bridge Drivers                                   | . 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SmartFusion2 Advanced Development Kit Setup                  | . 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SPI Flash Loader and Code Shadowing Demo Window              | . 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Starting the Demo                                            | . 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Wrong Device or Option Message                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Flash Loading                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Running the Target Application Image from DDR3 Memory        | . 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Timer and Interrupt Messages in Serial Console               | . 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Starting the Demo                                            | . 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Flash Loading                                                | . 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Running the Target Application Image from DDR3 Memory        | . 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| General DDR Configuration Settings                           | . 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DDR Memory Initialization Settings                           | . 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DDR Memory Timing Settings                                   | . 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Adding SoftConsole Installation Path                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

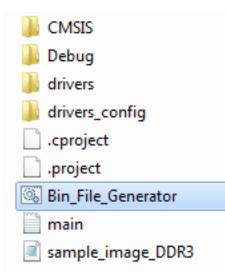

| Bin File Generator                                           | . 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                              | Code Shadowing – Multi Stage Boot Process Demo Block Diagram         Design Flow for Multi-Stage Boot Process Method         Code Shadowing – Hardware Boot Engine Demo Block Diagram         Top-Level Block Diagram         Design Flow for Hardware Boot Engine Method         USB to UART Bridge Drivers         SmartFusion2 Advanced Development Kit Setup         SPI Flash Loader and Code Shadowing Demo Window         Starting the Demo         Wrong Device or Option Message         Flash Loading         Running the Target Application Image from DDR3 Memory         Timer and Interrupt Messages in Serial Console         Starting the Demo         Flash Loading         Running the Target Application Image from DDR3 Memory         General DDR Configuration Settings         DDR Memory Initialization Settings         DDR Memory Timing Settings         Adding SoftConsole Installation Path |

# **Tables**

| Table 1. | Design Requirements                                   | 7    |

|----------|-------------------------------------------------------|------|

| Table 2. | SmartFusion2 Advanced Development Kit Jumper Settings | . 14 |

# 1 Preface

## 1.1 Purpose

This demo is for SmartFusion<sup>®</sup>2 system-on-chip (SoC) field programmable gate array (FPGA) devices. It provides instructions on how to use the corresponding reference design.

### 1.2 Intended Audience

This demo guide is intended for:

- FPGA designers

- Embedded designers

- System-level designers

### 1.3 References

See the following web page for a complete and up-to-date listing of SmartFusion2 device documentation: http://www.microsemi.com/products/fpga-soc/soc-fpga/smartfusion2#documentation

The following documents are referred in this demo guide.

- UG0331: SmartFusion2 Microcontroller Subsystem User Guide

- SmartFusion2 System Builder User Guide

### 2.1 Introduction

This demo design shows SmartFusion2 SoC FPGA device capabilities for code shadowing from the serial peripheral interface (SPI) flash memory device to double data rate (DDR) synchronous dynamic random access memory (SDRAM) and executing the code from DDR SDRAM.

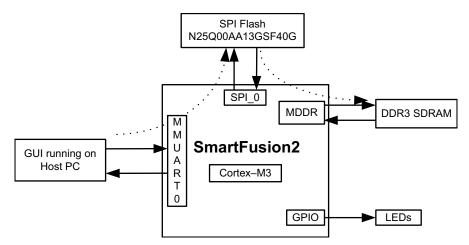

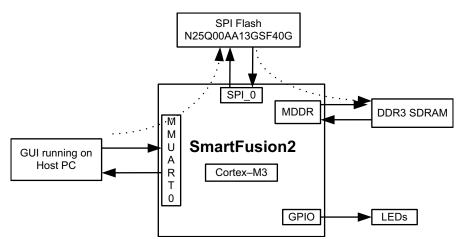

Figure 1 shows the top-level block diagram for code shadowing from SPI flash device to DDR memory.

#### Figure 1 • Top-Level Block Diagram

Code shadowing is a booting method that is used to run an image from external, faster, and volatile memories (DRAM). It is the process of copying the code from non-volatile memory to the volatile memory for execution.

Code shadowing is required when the non-volatile memory associated with a processor does not support random access to the code for execute-in-place, or there is insufficient non-volatile random access memory. In performance-critical applications, the execution speed can be improved by code shadowing, where code is copied to higher throughput RAM for faster execution.

Single data rate (SDR)/DDR SDRAM memories are used in applications that have a large application executable image and require higher performance. Typically, the large executable images are stored in non-volatile memory, such as NAND flash or SPI flash, and copied to volatile memory, such as SDR/DDR SDRAM memory, at power up for execution.

SmartFusion2 SoC FPGA devices integrate fourth generation flash-based FPGA fabric, an

ARM<sup>®</sup> Cortex<sup>®</sup>-M3 processor, and high performance communication interfaces on a single chip. The high speed memory controllers in the SmartFusion2 SoC FPGA devices are used to interface with the external DDR2/DDR3/LPDDR memories. The DDR2/DDR3 memories can be operated at a maximum speed of 333 MHz. The Cortex-M3 processor can directly run the instructions from external DDR memory through the microcontroller subsystem (MSS) DDR (MDDR). The FPGA cache controller and MSS DDR bridge handle the data flow for a better performance.

## 2.2 Design Requirements

Table 1 shows the design requirements for this demo.

#### Table 1 • Design Requirements

| Design Requirements                                                                                      | Description                                                                                   |  |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|

| Hardware Requirements                                                                                    |                                                                                               |  |

| SmartFusion2 Advanced Development Kit:<br>• 12 V adapter<br>• FlashPro5<br>• USB A to Mini - B USB cable | Rev A or later                                                                                |  |

| Desktop or Laptop                                                                                        | Windows XP SP2 Operating System - 32-bit/64-bit<br>Windows 7 Operating System - 32-bit/64-bit |  |

| Software Requirements                                                                                    |                                                                                               |  |

| Libero <sup>®</sup> System-on-Chip (SoC)                                                                 | v11.7                                                                                         |  |

| FlashPro Programming Software                                                                            | v11.7                                                                                         |  |

| SoftConsole                                                                                              | v3.4 SP1*                                                                                     |  |

| PC Drivers                                                                                               | USB to UART drivers                                                                           |  |

| Microsoft .NET Framework 4 client for<br>launching demo GUI                                              | _                                                                                             |  |

#### v4.0 and Libero SoC v11.7 Tutorial.

## 2.3 Demo Design

### 2.3.1 Introduction

The demo design files are available for download from the following path in the Microsemi website: *http://soc.microsemi.com/download/rsc/?f=m2s\_dg0386\_liberov11p7\_df*

The demo design files include:

- Libero SoC project

- STAPL programming files

- GUI executable

- Sample application images

- Linker scripts

- DDR configuration files

- Readme.txt file

See the <code>readme.txt</code> file provided in the design files for the complete directory structure.

### 2.3.2 Description

This demo design implements code shadowing technique to boot the application image from DDR memory. This design also provides host interface over SmartFusion2 SoC FPGA multi-mode universal asynchronous/synchronous receiver/transmitter (MMUART) to load the target application executable image into SPI flash connected to the MSS SPI0 interface.

The code shadowing is implemented in the following two methods:

- 1. Multi-stage boot process method using the Cortex-M3 processor

- 2. Hardware boot engine method using the FPGA fabric

### 2.3.2.1 Multi-Stage Boot Process Method

The application image is run from external DDR memories in the following two boot stages:

- The Cortex-M3 processor boots the soft boot loader from embedded non-volatile memory (eNVM), which performs the code image transfer from SPI flash device to DDR memory.

- The Cortex-M3 processor boots the application image from DDR memory.

This design implements a bootloader program to load the target application executable image from SPI flash device to DDR memory for execution. The bootloader program running from eNVM jumps to the target application stored in DDR memory after the target application image is copied to DDR memory.

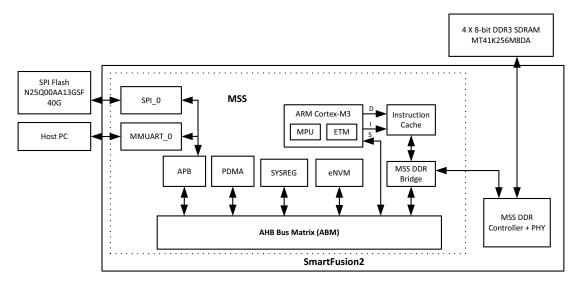

Figure 2 shows the detailed block diagram of the demo design.

#### Figure 2 • Code Shadowing – Multi Stage Boot Process Demo Block Diagram

The MDDR is configured for DDR3 to operate at 320 MHz. "Appendix: DDR3 Configurations" on page 22 shows the DDR3 configuration settings. DDR is configured before executing the main application code.

#### 2.3.2.1.1 Bootloader

The bootloader performs the following operations:

- 1. Copying the target application image from SPI flash memory to DDR memory.

- 2. Remapping the DDR memory starting address from 0xA0000000 to 0x00000000 by configuring the DDR\_CR system register.

- Initializing the Cortex-M3 processor stack pointer as per the target application. The first location of the target application vector table contains the stack pointer value. The vector table of the target application is available starting from the address 0x00000000.

- 4. Loading the program counter (PC) to reset handler of the target application for running the target application image from the DDR memory. Reset handler of the target application is available in the vector table at the address 0x00000004.

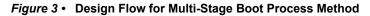

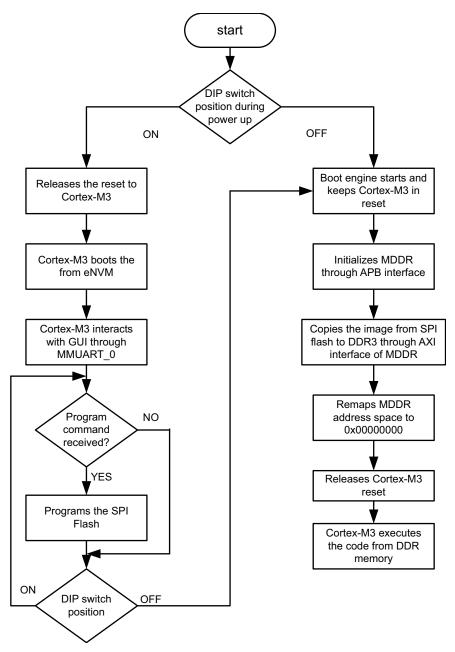

Figure 3 shows the demo design.

#### 2.3.2.1.2 Hardware Boot Engine Method

In this method, the Cortex-M3 directly boots the target application image from external DDR memories. The hardware boot engine copies the application image from the SPI flash device to DDR memory, before releasing the Cortex-M3 processor reset. After releasing the reset, the Cortex-M3 processor boots directly from DDR memory. This method requires less boot-up time than multi-stage boot process as it avoids multiple boot stages and copies application image to DDR memory in less time.

This demo design implements boot engine logic in FPGA fabric to copy the target application executable image from SPI flash to the DDR memory for execution. This design also implements SPI flash loader, which can be executed by Cortex-M3 processor to load the target application executable image into SPI flash device using the provided host interface over SmartFusion2 SoC FPGA MMUART\_0. The DIP switch1 on the SmartFusion2 Advanced Development Kit can be used to select whether to program the SPI flash device or to execute the code from DDR memory.

If the executable target application is available in the SPI flash device, the code shadowing from the SPI flash device to DDR memory is started on device power-up. The boot engine initializes the MDDR, copies the Image from SPI flash device to DDR memory, and remaps the DDR memory space to 0x00000000 by keeping the Cortex-M3 processor in reset. After boot engine releases the Cortex-M3 reset, the Cortex-M3 executes the target application from DDR memory.

The FIC\_0 is configured in Slave mode to access the MSS SPI\_0 from FPGA fabric AHB master. The MDDR AXI interface (DDR\_FIC) is enabled to access the DDR memory from FPGA fabric AXI master.

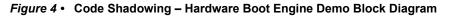

Figure 4 shows the detailed block diagram of the demo design.

#### 2.3.2.1.3 Boot Engine

This is the major part of the code shadowing demo that copies the application image from the SPI flash device to the DDR memory. The boot engine performs the following operations:

- 1. Initializing MDDR for accessing DDR3 at 320 MHz by keeping the Cortex-M3 processor in reset.

- 2. Copying the target application image from SPI flash memory device to DDR memory using the AXI master in the FPGA fabric through the MDDR AXI interface.

- 3. Remapping the DDR memory starting address from 0xA0000000 to 0x00000000 by writing to the DDR\_CR system register.

- 4. Releasing reset to Cortex-M3 processor to boot from DDR memory.

Figure 5 shows the demo design flow.

#### Figure 6 • Design Flow for Hardware Boot Engine Method

### 2.3.3 Creating Target Application Image for DDR Memory

An image that can be executed from the DDR memory is required to run the demo. Use the "productionexecute-in-place-externalDDR.Id" linker description file that is included in the design files to build the application image. The linker description file defines the DDR memory starting address as 0x00000000 since the bootloader/boot engine performs the DDR memory remapping from 0xA0000000 to 0x00000000. The linker script creates an application image with instructions, data, and BSS sections in memory whose starting address is 0x0000000. A simple light-emitting diode (LED) blinking, timer and switch based interrupt generation application image file is provided for this demo.

### 2.3.4 SPI Flash Loader

The SPI flash loader is implemented to load the on-board SPI flash memory with the executable target application image from the host PC through the MMUART\_0 interface. The Cortex-M3 processor makes a buffer for the data coming over the MMUART\_0 interface and initiates the peripheral DMA (PDMA) to write the buffered data into SPI flash through the MSS\_SPI0.

## 2.4 Running the Demo

The demo shows how to load the application image in the SPI flash and execute that application image from external DDR memories. It provides an example application image "sample\_image\_DDR3.bin". This image shows the welcome messages and timer interrupt message on the serial console and blinks LED1 to LED8 on the SmartFusion2 Advanced Development Kit. To see the GPIO interrupt messages on the serial console, press **SW2** or **SW3** switch.

## 2.5 Setting Up the Demo Design

The following steps describe how to setup the demo for SmartFusion2 Advanced Development Kit board:

- 1. Connect the Host PC to the J33 Connector using the USB A to mini-B cable. The USB to UART bridge drivers are automatically detected. Verify if the detection is made in the device manager as shown in Figure 7.

- 2. If USB drivers are not detected automatically, install the USB driver.

- 3. For serial terminal communication through the FTDI mini USB cable, install the FTDI D2XX driver. Download the drivers and installation guide from:

http://www.microsemi.com/soc/documents/CDM\_2.08.24\_WHQL\_Certified.zip.

#### Figure 7 • USB to UART Bridge Drivers

| 🚔 Device Manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                   |                                                                                                                                                                                                                                                                                                                                        |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| File Action View Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                   |                                                                                                                                                                                                                                                                                                                                        |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>辰</b> 15                                                                       |                                                                                                                                                                                                                                                                                                                                        |        |

| Image: Second stress       Image: Second stress         Image: Second |                                                                                   | FlashPro5 Port (COM47) Properties         General       Pot Settings         Driver       Details         FlashPro5 Port (COM47)         Device type:       Ports (COM & LPT)         Manufacturer:       Microsemi         Location:       on USB FP5 Serial Converter C         Device status       This device is working property. | ×      |

| FlashPro5 Port (COM4)     FlashPro5 Port (COM4)     FlashPro5 Port (COM4)     FlashPro5 Port (COM48)     FlashPro5 Port (COM48)     FlashPro5 Port (COM48)     Sound, video and game co     Sound, video and game co     System devices     Joint System devices     Joint System Serial Bus control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | M1) Update Driver Software Disable Uninstall Scan for hardware changes Properties | ОК (                                                                                                                                                                                                                                                                                                                                   | Cancel |

| Opens property sheet for the current select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ion.                                                                              |                                                                                                                                                                                                                                                                                                                                        |        |

4. Connect the jumpers on the SmartFusion2 Advanced Development Kit board, as shown in Table 2. **Caution:** Switch **OFF** the power supply switch, **SW7** while connecting the jumpers.

| Jumper                | Pin (From) | Pin (To) | Comments                                                            |

|-----------------------|------------|----------|---------------------------------------------------------------------|

| J116, J353, J354, J54 | 1          | 2        | These are the default jumper settings of the Advanced               |

| J123                  | 2          | 3        | Development Kit Board. Make sure these jumpers are set accordingly. |

| J124, J121, J32       | 1          | 2        | JTAG programming through FTDI                                       |

| J118, J119            | 1          | 2        | Programming SPI Flash                                               |

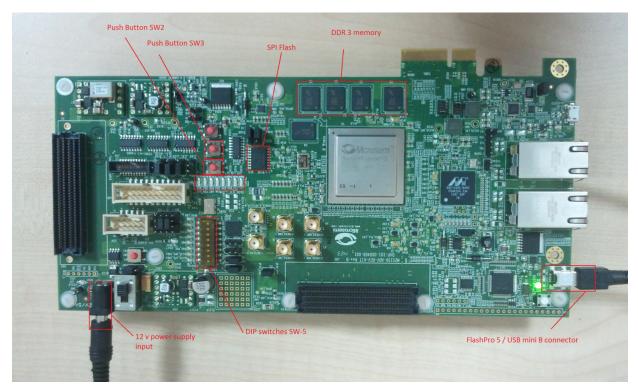

5. In the SmartFusion2 Advanced Development Kit, connect the power supply to the J42 connector. Figure 8. shows the board setup for running the code shadowing from SPI flash to DDR3 demo on the SmartFusion2 Advanced Development Kit.

Figure 8 • SmartFusion2 Advanced Development Kit Setup

Power Matters."

### 2.5.1 SPI Flash Loader and Code Shadowing Demo GUI

The GUI is required to run the code shadowing demo. SPI Flash Loader and Code Shadowing Demo GUI is a simple graphic user interface that runs on the host PC to program the SPI flash and runs the code shadowing demo on the SmartFusion2 Advanced Development Kit. UART is a communication protocol between the host PC and SmartFusion2 Advanced Development Kit. It also provides the Serial Console section to print the debug messages received from the application over the UART interface.

Figure 9. shows the SPI Flash Loader and Code Shadowing Demo Window.

Figure 9 • SPI Flash Loader and Code Shadowing Demo Window

| SPI Flash Loader and Code Shadowing Demo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Serial Port Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Serial Console             |

| COM Port COM1  Baud Rate 115200  Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |

| File Location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |

| Location Browse for binary image file Browse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |

| Address 00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |

| Code Shadowing Method<br>Multi-Stage Boot Process<br>Multi-Stage Boot |                            |

| Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |

| Program SPI Flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |

| Program and Code Shadowing from SPI Flash to DDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |

| <ul> <li>Program and Code Shadowing from SPI Flash to SDR</li> <li>Code Shadowing to DDR</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |

| <ul> <li>Code Shadowing to SDR</li> <li>Code Shadowing to SDR</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |