## SmartTime Tutorial Libero SoC for ProASIC3

NOTE: PDF files are intended to be viewed on the printed page; links and cross-references in this PDF file may point to external files and generate an error when clicked. View the online help included with software to enable all linked content.

## **Table of Contents**

| 32-Bit Shift Register                                                       | 7  |

|-----------------------------------------------------------------------------|----|

| Set Up Your Libero Project for 32-Bit Shift Register with Clock Enable      | 7  |

| Add a Clock Constraint - 32 Bit Example                                     | 11 |

| Run Place and Route                                                         | 13 |

| Maximum Delay Analysis with Timing Analyzer- 32-Bit Example                 | 15 |

| Minimum Delay Analysis with Timing Analyzer - 32-Bit Example                | 18 |

| Changing Constraints and Observing Results - 32-Bit Example                 | 19 |

| Design Using Both Clock Edges                                               | 21 |

| Import the EDIF Netlist - Design Uses Both Clock Edges                      | 21 |

| Add a Clock Constraint - Design Uses Both Clock Edges                       | 22 |

| Run Place and Route for a Design that Uses Both Clock Edges                 | 23 |

| Maximum Delay Analysis with Timing Analyzer - Design Using Both Clock Edges | 24 |

| Cross Probing with SmartTime - Design Using Both Clock Edges                | 25 |

| Generate a Timing Report - Design Uses Both Clock Edges                     | 27 |

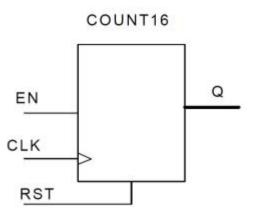

| 16-Bit Binary Counter Example                                               | 30 |

| Import the 16-Bit Binary Counter Example Design Source File                 | 30 |

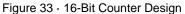

| Import a Timing Constraint File                                             | 31 |

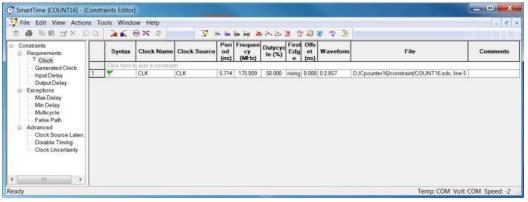

| Add an Input Delay Constraint                                               | 32 |

| Add an Output Delay Constraint                                              | 36 |

| Place and Route the 16-Bit Binary Counter Design                            | 38 |

| Using Filters and Creating Analysis Sets - 16-Bit Binary Counter Example    | 38 |

| False Path Constraints                                                      | 40 |

| Import the FALSE_PATH File and Add A Constraint                             | 40 |

| Place and Route Your FALSE_PATH Design                                      | 41 |

| Timing Analysis - Maximum Clock Frequency                                   | 42 |

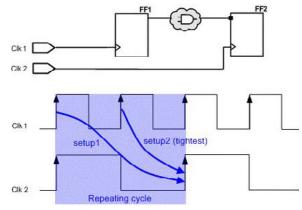

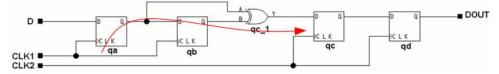

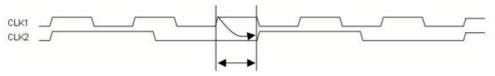

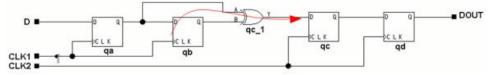

| Cross Clock Domain Analysis                                                 | 46 |

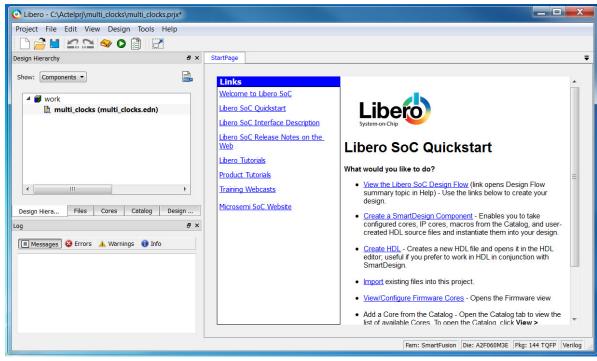

| Import EDN File and Run Compile for Cross Clock Domain Analysis Example     | 47 |

| Enter Timing Constraints for the Cross Clock Domain Analysis Example        | 49 |

| Place and Route Your Cross Clock Domain Analysis Example                    | 50 |

| Analyze Inter-Clock Domain Timing                                           | 51 |

| Product Support                                                             | 54 |

| Contacting the Customer Technical Support Center                            | 54 |

| Non-Technical Customer Service                                              | 54 |

The following tutorials explore common SmartTime features with example designs:

- <u>32-Bit Shift Register with Clock Enable</u>

- Design Using Both Clock Edges

- <u>16-Bit Binary Counter</u>

- False Path Constraints

- <u>Cross Clock Domain Analysis</u>

Many actions described in the tutorials can be performed from the menus or in the SmartTime Toolbar. The table below lists all the SmartTime Toolbar actions.

| Table 1 · SmartTime Toolbar |

|-----------------------------|

|                             |

| lcon          | Description                                              |

|---------------|----------------------------------------------------------|

| 8             | Commits the changes                                      |

| 4             | Prints the contents of the constraints editor            |

|               | Copies data to the clipboard                             |

| Ē             | Pastes data from the clipboard                           |

|               | Modifies the selected object from the constraints editor |

| ×             | Deletes the selected object from the constraints editor  |

| 2             | Undoes previous changes                                  |

| <u>c</u>      | Redoes previous changes                                  |

| $\leq$        | Opens the maximum delay analysis view                    |

| $\leq$        | Opens the minimum delay analysis view                    |

| <b>(b)</b>    | Opens the manage clock domains manager                   |

| ×             | Opens the path set manager                               |

| 2             | Recalculates all                                         |

| 37            | Opens the constraints editor                             |

| <del>ار</del> | Opens the add clock constraint dialog box                |

| Ťr.           | Opens the add generated clock constraint dialog box      |

| *<br>**       | Opens the set input delay clock constraint dialog box    |

| *∞            | Opens the set output delay clock constraint dialog box   |

| lcon       | Description                                                    |

|------------|----------------------------------------------------------------|

| 20.        | Opens the set false path constraint dialog box                 |

| ×          | Opens the set maximum delay constraint dialog box              |

| 2          | Opens the set minimum delay constraint dialog box              |

| N.         | Opens the set multicycle constraint dialog box                 |

| 5 <u>.</u> | Opens the set clock source latency dialog box                  |

| <b>1</b>   | Opens the set constraint to disable timing arcs dialog box     |

| <b>™</b>   | Opens the set clock-to-clock uncertainty constraint dialog box |

| ~~         | Checks timing constraints                                      |

| <u>B</u>   | Opens the constraint wizard                                    |

## **32-Bit Shift Register**

# Set Up Your Libero Project for 32-Bit Shift Register with Clock Enable

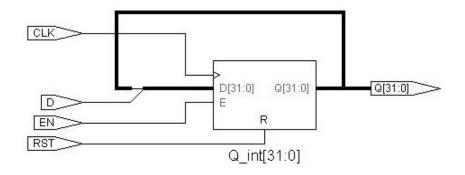

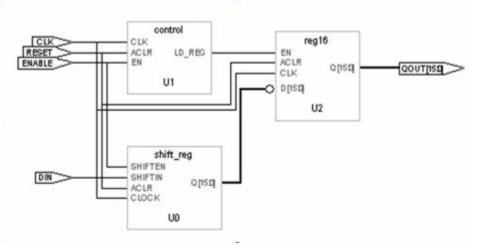

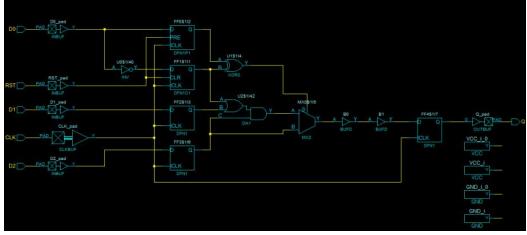

This tutorial section describes how to enter a clock constraint for the 32-bit shift register shown in the figure below. You will use the SmartTime Constraints Editor and perform post-layout timing analysis using the SmartTime Timing Analyzer.

Figure 1 · 32-Bit Shift Registers

Use the links below to go directly to a topic:

- Add a Clock Constraint 32 Bit Example

- Run Place and Route

- <u>Maximum Delay Analysis with Timing Analyzer- 32-Bit Example</u>

- Minimum Delay Analysis with Timing Analyzer 32-Bit Example

- Changing Constraints and Observing Results 32-Bit Example

#### To set up your project:

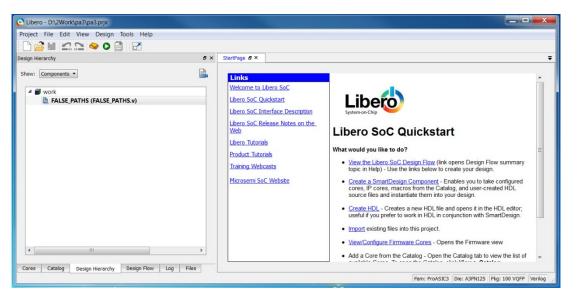

- 1. Invoke Libero SoC. From the Project menu, choose New Project.

- 2. Enter Shift32 for your new project name and browse to a folder for your project location. Enter the following values for the project settings (as shown in the figure below):

| New Project         |               |          |      |       |         |               |              |   |

|---------------------|---------------|----------|------|-------|---------|---------------|--------------|---|

| Project             |               |          |      |       |         |               |              |   |

| Enable Block C      | Creation      |          |      |       |         |               |              |   |

| Name:               |               |          |      |       | 1       |               |              |   |

| Location:           | D:            |          |      |       |         | Browse        |              |   |

| Prefered HDL type   |               | g 🔘 VHDL |      |       | Je.     |               |              |   |

| Description:        |               | , ()     |      |       |         | ÷             |              |   |

| Edit Tool Prof      | iles          |          |      |       |         | *             |              |   |

| Device              |               |          |      |       |         |               |              |   |

| Family:             | ProASIC3      | •        |      |       |         |               |              |   |

| Die:                | A3P060        | •        |      |       |         |               |              |   |

| Package:            | 100 VQFP      | •        |      |       |         |               |              |   |

| Speed:              | -2            | •        |      |       |         |               |              |   |

| Core Voltage (V):   | 1.5           | •        |      |       |         |               |              |   |

| Operating Condition | ons:          |          |      |       |         |               |              |   |

|                     |               | Range    | 9    | Best  | Typical | Worst         | -            |   |

| Junction Te         | mperature (C) | COM      | •    | 0     | 25      | 70            |              |   |

| Core Voltag         | ge (V)        | СОМ      | •    | 1.575 | 1.500   | 1.425         | ~            |   |

| Design Templates    |               |          |      |       |         |               |              |   |

|                     |               |          | Core | •     |         |               | Version      |   |

|                     |               |          |      |       |         |               |              |   |

|                     |               |          |      |       |         | a             |              |   |

|                     |               |          |      |       |         | Show only lat | est version  |   |

|                     |               |          |      | Ш     |         | Show only lat | test version | • |

Figure 2 · 32 Bit Shift Register Project Settings

- Family: ProAsic3

- Die: A3P060

- Package: 100 VQFP

- Speed: -2

- Die Voltage: 1.5 V

- All other fields: Use default values

- 3. Click **OK** to continue.

- 4. From the View menu, display the following windows (View > Windows > <window name>):

- Design Flow

- Design Hierarchy

- Files

- Log

- Search Results

- HDL Source Files

- 5. From the **File** menu, choose **Import > HDL Source File**s and import the Verilog file **shift\_reg32.v** for the 32-bit Shift Register.

After you import the file, confirm that the imported file appears in the Files window, as shown in the figure below.

| Files            |        |  |  |

|------------------|--------|--|--|

| 🗀 compone        | nt     |  |  |

| D 🗀 constraint   |        |  |  |

| 🖻 🗀 designer     |        |  |  |

| 🔺 🗀 hdl          |        |  |  |

| 🖹 shift_re       | eg32.v |  |  |

| 👂 🗀 simulatio    |        |  |  |

| 🗀 smartgen       |        |  |  |

| 🗀 stimulus       |        |  |  |

| Image: Synthesis |        |  |  |

| 👂 🗀 tooldata     |        |  |  |

|                  |        |  |  |

|                  |        |  |  |

|                  |        |  |  |

|                  |        |  |  |

|                  |        |  |  |

|                  |        |  |  |

|                  |        |  |  |

|                  |        |  |  |

|                  |        |  |  |

|                  |        |  |  |

|                  |        |  |  |

|                  |        |  |  |

Figure 3 · HDL File shift\_reg32.v in the Libero SoC File Window

Confirm that the shift\_reg32 design appears in the Design Hierarchy window, as shown in the figure below.

| esign Hierarchy             |   |

|-----------------------------|---|

| Show: Components 💌          |   |

| 4 🇰 work                    |   |

| shift_reg32 (shift_reg32.v) |   |

|                             |   |

|                             |   |

|                             |   |

|                             |   |

|                             |   |

|                             |   |

|                             |   |

|                             |   |

|                             |   |

|                             |   |

|                             |   |

|                             |   |

|                             |   |

|                             |   |

|                             |   |

|                             |   |

|                             |   |

|                             |   |

|                             |   |

|                             |   |

| < III                       | 4 |

|                             |   |

Figure 4 · shift\_reg32 in the Design Hierarchy Window

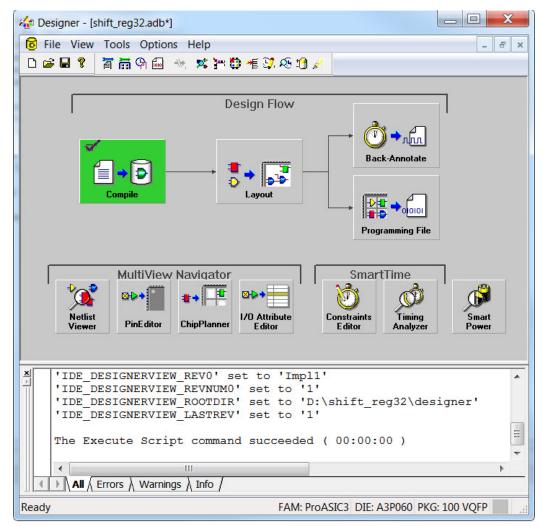

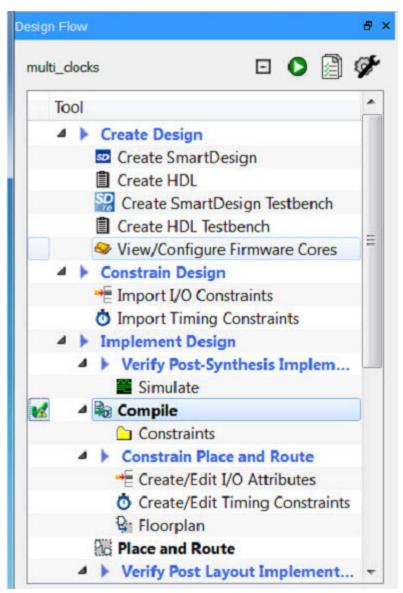

- 6. In the Design Flow window, double-click **Synthesize** to run Synplify Pro with default settings. A green check marks appears next to Synthesize when Synthesis is successful (as shown in the figure below).

- 7. Double-click **Compile** in the Design Flow window to run Compile with default settings. A green check mark appears next to Compile when it completes successfully (as shown in the figure below).

| Project File Edit View Design Tools H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | elp                                                                                                        |                                                                                                    |                                                                                            |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| □ 🚰 🗖 🗠 🗠 🗢 🙆 📑                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                            |                                                                                                    |                                                                                            |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

| esign Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ð×                                                                                                         | StartPage 🗗 🗙                                                                                      | Reports 5                                                                                  | ×                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

| shift_reg32   Tool  Tool  Simulate  Simulate  Simulate  Simulate  Simulate  Simulate  Simulate  Create Constraints  Simulate  Simulate  Configure Flash*Freeze  Design Hie Desig  Stimulus Hie Ca                                                                                                                                                                                                                                                                                                                                                                                       | ÷<br>talog                                                                                                 | shift_re<br>Synthesize<br>Synplif<br>shir<br>run_op<br>Compile<br>shift_re<br>shift_re<br>shift_re | 2<br>2322pinrpt<br>2322pinrpt<br>4<br>1000<br>1000<br>1000<br>1000<br>1000<br>1000<br>1000 | The<br>The<br>The<br>The<br>The<br>The<br>The<br>The<br>The<br>The | I O Errors ▲ 0 Warning ● 1 Info<br>'set_compile_info' command succeeded.<br>'set_compile_info' command succeeded. |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                            |                                                                                                    |                                                                                            |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8       |

| E Messages & Errors A Warning info<br>The 'set_compile_info' command suc<br>The 'set_compile_info' command suc<br>O INFO: No User PDC file(s) was sp<br>The 'compile' command succeeded.<br>The Execute Scribt command succeeded. | ceeded<br>ceeded<br>ceeded<br>ceeded<br>ceeded<br>ceeded<br>ceeded<br>ceeded<br>ceeded<br>ceeded<br>ceeded |                                                                                                    |                                                                                            |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A III A |

Figure 5 · Synthesis and Compile Complete - 32-Bit Shift Register with Clock Enable

## Add a Clock Constraint - 32 Bit Example

To add a clock constraint to your design:

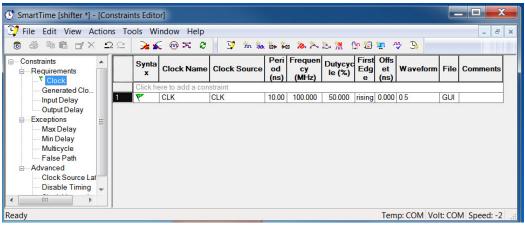

1. In the **Design Flow** window double-click **Create/Edit Timing Constraints** to open the Constraints Editor (as shown in the figure below). Designer opens before the Constraints Editor appears; minimize Designer and continue in the **Constraints Editor**.

| SmartTime [shift_reg32 *] - [Cor                                                                                                                             | straints Editor]                                                                                                                                                                                                                                                |                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 😳 File Edit View Actions To                                                                                                                                  | ols Window Help                                                                                                                                                                                                                                                 | _ & ×           |

| 0 🖨 🖬 🖥 🕁 X 🗅 🗅                                                                                                                                              | 😹 🐵 末 32 😏 施 施 施 施 施 為 為 急 烈 白 超 塑 🦈 🕒                                                                                                                                                                                                                          |                 |

| Constraints                                                                                                                                                  | Synta<br>x         Clock Name         Clock Source         Peri<br>od         Frequen<br>cy         Dutycyc<br>le (%)         First<br>Edg<br>e (ns)         Offs           (ns)         (MHz)         (ms)         (ms)         (ms)         (ms)         (ms) | File Comments   |

| Generated Clo<br>Input Delay<br>Output Delay<br>Exceptions ≡<br>Max Delay<br>Multicycle<br>False Path<br>Advanced<br>Clock Source Lat<br>Disable Timing<br>↓ | Click here to add a constraint                                                                                                                                                                                                                                  |                 |

| Ready                                                                                                                                                        | Temp: COM Volt                                                                                                                                                                                                                                                  | : COM Speed: -2 |

Figure 6 · SmartTime Constraints Editor

2. From the **Actions** menu, choose **Constraints > Clock** to open the Create Clock Constraint Editor, as shown in the figure below.

| Create Clock Co                            | onstraint                | x   |

|--------------------------------------------|--------------------------|-----|

| Clock                                      | CLK                      |     |

| Clock                                      |                          |     |

| T(zero)                                    |                          |     |

|                                            | Period: ns or Frequency: | MHz |

|                                            |                          |     |

| <ul> <li>Offset:</li> <li>0.000</li> </ul> | ns 50.0000 %             |     |

| Comment:                                   |                          |     |

|                                            |                          |     |

| Help                                       | OK Canc                  | el  |

- Figure 7 · Create Clock Constraint Dialog Box

- 3. Set the **Frequency** to **150 MHz** (as shown in the figure below) and leave all other values at the default setting. Click **OK** to continue.

| Create Clock Co           | onstraint |                 | The second |                   | X      |

|---------------------------|-----------|-----------------|------------|-------------------|--------|

| Clock<br>Clock<br>T(zero) | CLK       | – Period: 6.667 |            | or Frequency: 150 | MHz    |

| Comment:                  |           | Duty cycle:     |            |                   |        |

| Help                      |           |                 |            | ОК                | Cancel |

Figure 8 · Add a 150 MHz Clock Constraint

The clock constraint appears in the SmartTime Constraints Editor (as shown in the figure below).

| Constraints Editor                                                                                                                                 |   |            |                  |              |                    |                        |                   |                   |                    |           |      |          |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|------------------|--------------|--------------------|------------------------|-------------------|-------------------|--------------------|-----------|------|----------|

| □ Constraints □ Requirements □ Clock                                                                                                               |   | Synta<br>x | Clock Name       | Clock Source | Peri<br>od<br>(ns) | Frequen<br>cy<br>(MHz) | Dutycyc<br>le (%) | First<br>Edg<br>e | Offs<br>et<br>(ns) | Waveform  | File | Comments |

| Generated Clock                                                                                                                                    |   | Click he   | ere to add a con | straint      |                    |                        |                   |                   | 2010 - 1813)<br>7  | 5.<br>7.  |      |          |

| Input Delay                                                                                                                                        | 1 | ٣          | CLK              | CLK          | 6.667              | 150.000                | 50.000            | rising            | 0.000              | 0 3.33333 | GUI  |          |

| Exceptions     Max Delay     Min Delay     Multicycle     False Path     Advanced     Clock Source Laten.     Disable Timing     Clock Uncertainty |   |            |                  |              |                    |                        |                   |                   |                    |           |      |          |

Figure 9 · 150 MHz Clock Constraint in the Constraint Editor

- 5. From the  $\ensuremath{\textit{File}}$  menu, choose  $\ensuremath{\textit{Commit}}$  to save the constraints.

- $6. \quad \mbox{From the SmartTime File menu, choose Exit to continue.}$

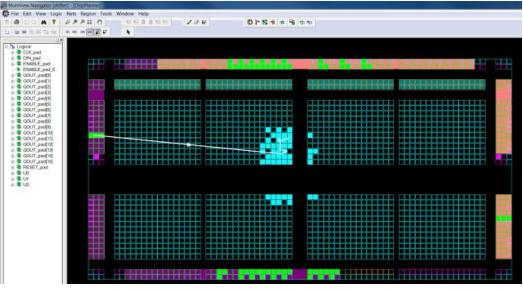

## **Run Place and Route**

You must run Place and Route from Designer. To do so:

1. View Designer, as shown in the figure below.

Figure 10 · Compile Complete, Ready for Layout

- 2. Click Layout.

- 3. Click the checkbox to enable **Timing-Driven** layout in Layout Options and leave the other values at the default settings (as shown in the figure below). Click **OK** to continue.

Maximum Delay Analysis with Timing Analyzer- 32-Bit Example

| Layout Options                | X      |

|-------------------------------|--------|

| ✓ Timing-driven               |        |

| Power-driven                  |        |

| Run place                     |        |

| Place incrementally           |        |

| Lock existing placement (Fix) |        |

| Run route                     |        |

| Route incrementally           |        |

|                               |        |

| 🔲 Use Multiple Passes         |        |

| Configure                     |        |

|                               |        |

| Advanced                      |        |

|                               |        |

| Help OK                       | Cancel |

|                               |        |

Figure 11 · Layout Options Dialog Box

The Layout button turns green to indicate that Layout has completed successfully.

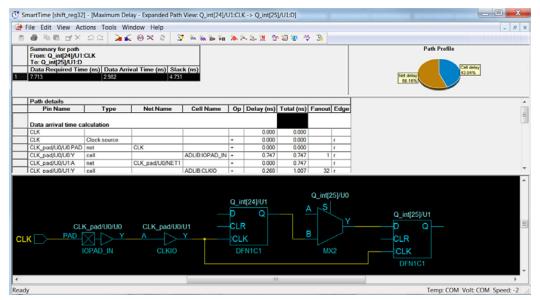

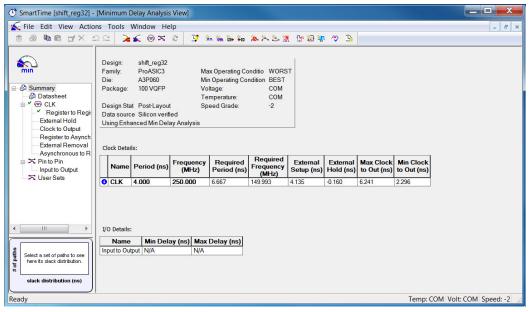

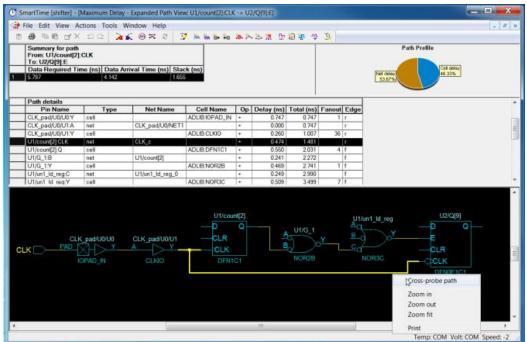

## Maximum Delay Analysis with Timing Analyzer- 32-Bit Example

The SmartTime Maximum Delay Analysis window displays the design maximum operating frequency and lists any setup violations.

#### To perform Maximum Delay Analysis:

1. Click the **Timing Analyzer** button in Designer to open SmartTime. The Maximum Delay analysis window appears (as shown in the figure below). A green check next to the clock name indicates there are no timing violations for that clock domain. The Summary page displays a summary of the clock domain timing performance.

The Maximum Delay Analysis Summary displays the:

- Maximum operating frequency for the design

- External setup and hold requirements

- Maximum and minimum clock-to-out times. In this example, the maximum clock frequency for CLK is 250 MHz.

| I SmartTime [shift_reg32] - [                                                                         | Maximum                                | Delay Analysi | s View]                                                    |                                                                                 |         |                        |                   |                  |             |             |              | x     |

|-------------------------------------------------------------------------------------------------------|----------------------------------------|---------------|------------------------------------------------------------|---------------------------------------------------------------------------------|---------|------------------------|-------------------|------------------|-------------|-------------|--------------|-------|

| Arile Edit View Action                                                                                | s Tools                                | Window He     | lp                                                         |                                                                                 |         |                        |                   |                  |             |             |              | e x   |

| 6 6 <b>6 6 7</b> × 9                                                                                  | 2 🛛 🔁                                  | ≲ 🐵 🌫         | 2 37 8                                                     | in 🐜 🗛 🌠                                                                        | ***     | l 📴 🕼 🙀                | 🗤 💃               |                  |             |             |              |       |

| MAX                                                                                                   | Data source<br>Using Enh<br>Clock Deta | Period (ns)   | Mir<br>Vo<br>Te<br>ed<br>ay Analysis<br>Frequency<br>(MHz) | n Operating Co<br>Itage:<br>mperature:<br>eed Grade:<br>Required<br>Period (ns) | (MHz)   | External<br>Setup (ns) | COLOR DISAS STATE | and street state | to Out (ns) |             |              |       |

| User Sets                                                                                             | CLK                                    | 4.000         | 250.000                                                    | 6.667                                                                           | 149.993 | 4.135                  | -0.160            | 6.241            | 2.296       |             |              |       |

| Illi       Select a set of paths to see<br>here its slack distribution.       Stack distribution (ns) | I/O Details<br>Name<br>Input to Ou     | Min Dela      | ay (ns) Max<br>N/A                                         | Delay (ns)                                                                      |         |                        |                   |                  |             |             |              |       |

| Ready                                                                                                 |                                        |               |                                                            |                                                                                 |         |                        |                   |                  | Temp: (     | COM Volt: ( | COM Speed: · | •2 at |

Figure 12 · Maximum Delay Analysis - Summary

- 2. Click the + sign next to CLK to expand the display and show the Register to Register, Input to Register and Register to Output path sets.

- 3. Select **Register to Register** to display the register-to-register paths. The window displays a list of register-to-register paths and detailed timing analysis for the selected path (as shown in the figure below). Note that all the slack values are positive, indicating that there are no setup time violations.

| a File Edit View Action a line interview inte |      | ools Window He                                              |               | ₩a ta ¥a ≫a      | 221     | N Cr 12         | ን 🚛 🛷            | 9             |                                       |              |              | -           | 5  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------|---------------|------------------|---------|-----------------|------------------|---------------|---------------------------------------|--------------|--------------|-------------|----|

| MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | From |                                                             |               |                  |         |                 | то *             |               |                                       |              |              |             |    |

| 이 없 Summary<br>-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | Source Pin                                                  | Sink          | Pin Dela<br>(ns) |         | Arrival<br>(ns) | Required<br>(ns) | Setup<br>(ns) | Apply Fi<br>Minimum<br>Period<br>(ns) | skew<br>(ns) | Store Filter | Reset Filte | er |

| Register to Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1    | Q_int[9]/U1:CLK                                             | Q_int[10]/U1  | :D 2.33          | 6 3.915 | 3.782           | 7.697            | 0.428         | 2.752                                 | -0.012       |              |             |    |

| External Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2    | Q_int[2]/U1:CLK                                             | Q_int[3]/U1:E | 2.09             | 5 4.120 | 3.569           | 7.689            | 0.428         | 2.547                                 | 0.024        | -            |             |    |

| Clock to Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3    | Q_int[8]/U1:CLK                                             | Q_int[9]/U1:E | 2.06             | 8 4.164 | 3.521           | 7.685            | 0.428         | 2.503                                 | 0.007        |              |             |    |

| Register to Asynch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4    | Q_int[4]/U1:CLK                                             | Q_int[5]/U1:0 | 2.07             | 5 4.174 | 3.525           | 7.699            | 0.428         | 2.493                                 | -0.010       |              |             |    |

| External Recove                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5    | Q_int[26]/U1:CLK                                            | Q_int[27]/U1  | D 2.06           | 6 4.183 | 3.510           | 7.693            | 0.428         | 2.484                                 | -0.010       |              |             |    |

| Asynchronous to R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6    | Q_int[1]/U1:CLK                                             | Q_int[2]/U1:E | 2.05             | 4 4.210 | 3.503           | 7.713            | 0.428         | 2.457                                 |              |              |             |    |

| □ In to Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7    | Q_int[16]/U1:CLK                                            | Q_int[17]/U1  |                  |         | 3.429           | 7.703            | 0.428         | 2.393                                 |              |              |             |    |

| Input to Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8    | Q_int[3]/U1:CLK                                             | Q_int[4]/U1:0 |                  | 3 4.286 | 3.403           | 7.689            | 0.428         | 2.381                                 | 0.000        |              |             |    |

| Ser Sets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9    | Q_int[10]/U1:CLK                                            | Q_int[11]/U1  |                  |         | 3.394           | 7.725            | 0.428         | 2.336                                 |              |              |             |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10   | Q intf51/U1·CLK                                             | Q intf61/U11  | ) 189            | 7 4 342 | 3 357           | 7 699            | 0 428         | 2 325                                 | 0.000        |              |             |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | Details for path<br>From: Q_int[9]/U1<br>To: Q_int[10]/U1:[ |               |                  |         |                 |                  |               |                                       |              |              |             |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | Pin Nar                                                     | ne            | Туре             | Ne      | t Name          | Cell             | Name          | Op Del                                | ay (ns)      | Total (ns)   | Fanout Edg  | je |

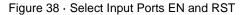

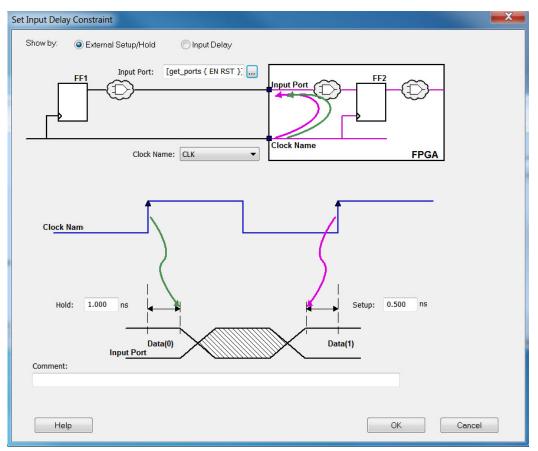

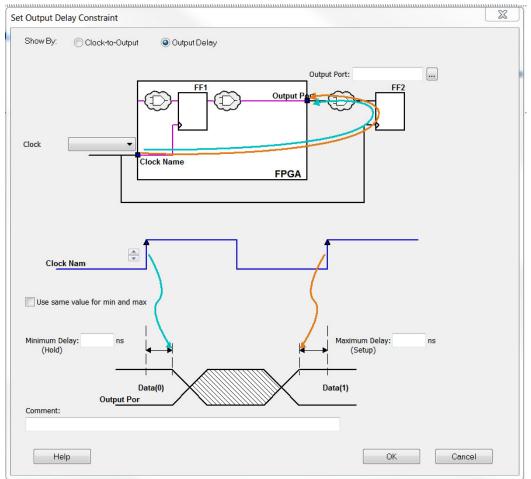

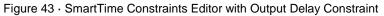

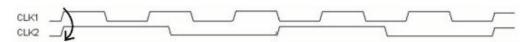

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |                                                             |               |                  |         |                 |                  |               |                                       |              |              |             |    |