## **Axcelerator Starter Kit**

## User's Guide v1.1

#### Actel Corporation, Mountain View, CA 94043

© 2005 Actel Corporation. All rights reserved.

Printed in the United States of America

Part Number: 50200037-1/02.05

Release: February 2005

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

#### Trademarks

Actel and the Actel logo are registered trademarks of Actel Corporation.

Adobe and Acrobat Reader are registered trademarks of Adobe Systems, Inc.

All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

## **Table of Contents**

|   | Introduction       5         Document Organization       5         Document Assumptions       5                                                                                                                                                                                                                                                                                                       |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Setup and Self-Test       7         LVDS DDR Loopback Circuit       7         Switches and LEDs Circuit       8         Using and Testing the Example Design       8                                                                                                                                                                                                                                  |

| 2 | Hardware Description       13         Axcelerator Evaluation Board Components       13         LVDS Connections       15         LED Device Connections       16         Switch Device Connections       16         Headers       17                                                                                                                                                                  |

| 3 | Tutorial19Step 1 – Create a New Project19Step 2 – Add ACTgen Components24Step 3 – Perform a Pre-Synthesis Simulation27Step 4 – Synthesize the Design in Synplify®43Step 5 – Perform a Post-Synthesis Simulation46Step 6 – Implement the Design Using Designer46Step 7 – Perform a Timing Simulation with Back-Annotated Timing56Step 8 – Generate the Programming File56Step 9 – Program the Device57 |

| A | Board Connections                                                                                                                                                                                                                                                                                                                                                                                     |

| B | P160 Connections                                                                                                                                                                                                                                                                                                                                                                                      |

| С | Board Schematic                                                                                                                                                                                                                                                                                                                                                                                       |

| D | Product Support                                                                                                                                                                                                                                                                                                                                                                                       |

#### Table of Contents

| Customer Service                                 |

|--------------------------------------------------|

| Actel Customer Technical Support Center          |

| Actel Technical Support                          |

| Website                                          |

| Contacting the Customer Technical Support Center |

|                                                  |

| Index                                            |

## Introduction

Thank you for purchasing the Actel Axcelerator (AX) Starter Kit.

This guide provides you with the information you need to easily evaluate Axcelerator devices.

### **Document Organization**

The Axcelerator Starter Kit contains the following chapters:

Chapter 1 – "Setup and Self-Test" describes how to setup the Axcelerator Evaluation Board and how to perform a self test.

Chapter 2 – "Hardware Description" describes the components on the Axcelerator Evaluation Board.

Chapter 3 - "Tutorial" contains a nine-step process that illustrates a basic Verilog design.

Appendix A - "Board Connections" contains a table listing the board connections.

Appendix B - "P160 Connections" contains a table listing the P160 connections.

Appendix C - "Board Schematic" shows the schematic of the Axcelerator Evaluation Board.

Appendix D - "Product Support" describes our support services.

### **Document Assumptions**

This user's guide assumes the following:

- You intend to use Actel Libero® Integrated Design Environment (IDE) software.

- · You have installed and are familiar with Actel Libero IDE software.

- You are familiar with the Verilog hardware description language.

- You are familiar with UNIX workstations and operating systems or PCs and Windows<sup>®</sup> operating systems.

## **Setup and Self-Test**

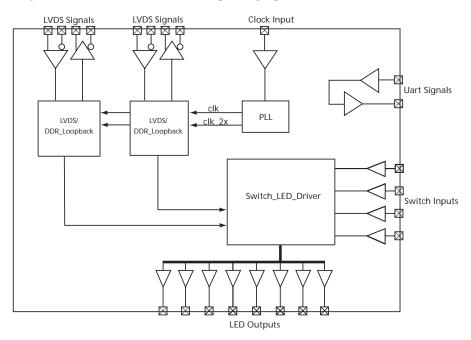

This chapter describes how to set up the Axcelerator Evaluation Board and how to perform a self-test. Figure 1-1 shows an AX Starter Kit example design specification.

Figure 1-1. Design Specification

## LVDS DDR Loopback Circuit

The AX Starter Kit example design contains a self-checking serial loopback circuit. This circuit uses the AX chip's Double Data Rate (DDR) functionality to transmit and receive data at 80 MHz. This is double the 40 MHz clocking rate of the rest of the system. When functioning, the circuit periodically sends a ten-bit test pattern (0101110011) at 80 Megabits per second. See the enclosed Verilog files for an example of using DDR and Low Voltage Differential Signaling (LVDS) I/Os. If a cable is connected from the LVDS outputs to the LVDS inputs, the circuit runs and an LED begins blinking to verify that the data is being transmitted and received correctly. If the I/Os are not connected or if there is another problem, the LED will not light up. There are two identical LVDS/DDR loopback circuits in the example design. One displays its status on LED[8] and is wired to the

Setup and Self-Test

SMA connectors on the board. The other is wired only to jumpers, and its status is displayed on LED[7].

### Switches and LEDs Circuit

Table 1-1 will help in understanding the behavioral relationships between each of the switches and indications on the various LEDS.

| Switch    | Description                                                                                                                                                                                           |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWITCH[1] | Asynchronously turns on LEDs[8:2] while held. Sets LEDs[6:2] to <b>01010</b> for a short period when released.                                                                                        |

| SWITCH[2] | Asynchronously turns off all LEDs[8:2] while held. Sets LEDs[6:2] to <b>10101</b> for a short period when released.                                                                                   |

| SWITCH[3] | Sets LEDs[6:2] to begin a standard binary counting pattern. Any<br>other switch overrides the counting mode. (The behavior of<br>SWITCH[3] is the default behavior if you do not press any switches.) |

| SWITCH[4] | Reset. Asynchronous reset for all logic. Also turns all LEDs[8:1] on while held.                                                                                                                      |

| Table 1-1 | Switches | and LEDs |

|-----------|----------|----------|

|-----------|----------|----------|

### Using and Testing the Example Design

This section describes using and testing the example design (AXEV\_TOPPLACE\_REV2\_SEP28.pdf).

## To verify that the design/board is programmed correctly, powered-up, and running:

1. Set up loopback on both LVDS (TX, RX) signal pairs via shunts placed on JP36 and JP37.

On header JP36:

- Using a shunt, connect RX2P to TX2P; i.e., receive 2 positive to transmit 2 positive. (Connect header pin 2 to pin 1 on JP36.)

- Using a shunt, connect RX2N to TX2N; i.e., receive 2 negative to transmit 2 negative. (Connect header pin 4 to pin 3 on header JP36.)

On header JP37:

- Using a shunt, connect RX1P to TX1P; i.e., receive 1 positive to transmit 1 positive. (Connect header pin 3 to pin 1 on JP37.)

- Using a shunt, connect RX1N to TX1N; i.e., receive 1 negative to transmit 1 negative. (Connect pin 4 to pin 2 on header JP37.)

- 2. Using a multimeter, test the impedance between power and ground for each voltage plane.

The reading should be taken between the test points labelled 3.3 V, 2.5 V. 1.8 V and 1.5 V and the test points labelled ground. A high reading is to be expected for all power/ground planes. If a short is detected (indicated by a low impedance reading of less than 1 W), do not proceed further.

3. Attach 9 V DC power to the Board at J1.

Plug the 9 V DC supply cable into the power plug on the back of the board.

4. Press SW4 and verify that all LEDs go high (turn on). Verify that LEDs[6:1] go low (turn off) when SW4 is released.

Note: LEDs[8:7] may stay on.

- 5. Press SW1 and verify that LEDs[8:2] turn on. When you release SW1, verify that LEDs[6:2] display 01010 for a short time (0 indicates the LED is off, 1 indicates the LED is on).

- 6. Press SW2 and verify that LEDs[8:2] turn off. When you release SW2, verify that LEDs[6:2] display 10101 for a short time.

- 7. Press SW3 and verify that LEDs[6:2] begin counting in a standard binary counting sequence.

- 8. Provided loopback cables are connected to the SMA connectors, or loopback shunts are connected to the headers JP36 and JP37 (as in step 1), the LVDS loopback status may be observed. Observe the LVDS/DDR loopback status by verifying that LED[8] and LED[7] are blinking.

Table 1-2 shows the Design Pin Description.

| Name   | Pin<br>Number | Pin Type    | Description                                                                             |

|--------|---------------|-------------|-----------------------------------------------------------------------------------------|

| CLK_in | 76            | LVTTL Input | 40 MHz clock input to PLL. This will be used to generate 40 and 80 MHz internal clocks. |

Table 1-2. Design Pin Description

#### Setup and Self-Test

| Name       | Pin<br>Number | Pin Type        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|---------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED_out[1] | 123           | LVTTL<br>Output | Driver for LED_1. This LED will be driven<br>low unless the reset switch is active. In this<br>case LED_1 will be driven high<br>asynchronously.                                                                                                                                                                                                                                                                                                                                                                                                            |

| LED_out[2] | 122           | LVTTL<br>Output | Driver for LED_2. Asynchronously driven<br>high by reset or SWITCH[1].<br>Asynchronously driven low by SWITCH[2].<br>If the clock circuit is functioning when the<br>switch is released, the LED will be set as one<br>of the following states.<br>SWITCH[1] – LEDs[6:2] display <b>01010</b> for<br>approximately 1 second, then return to 0.<br>SWITCH[2] – LEDs[6:2] display <b>10101</b> for<br>approximately 1 second then return to 0.<br>SWITCH[3] – LEDs[6:2] begin a counting<br>pattern. Counting continues until any other<br>switch is touched. |

| LED_out[3] | 121           | LVTTL<br>Output | See LED_out[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LED_out[4] | 120           | LVTTL<br>Output | See LED_out[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LED_out[5] | 109           | LVTTL<br>Output | See LED_out[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LED_out[6] | 108           | LVTTL<br>Output | See LED_out[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### Table 1-2. Design Pin Description (Continued)

# Using and Testing the Example Design

| Name         | Pin<br>Number | Pin Type        | Description                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED_out[7]   | 107           | LVTTL<br>Output | Driver for LED_7. This LED will be driven<br>high asynchronously by either reset or<br>SWITCH[1]. After reset the LED will<br>remain on briefly, then act as the status light<br>for the LVDS loopback circuit 2. If the<br>loopback circuit is functioning properly, this<br>LED will flash. Otherwise, this LED will be<br>off. (This circuit is connected to test header<br>JP36.)                                       |

| LED_out[8]   | 106           | LVTTL<br>Output | Driver for LED_8. This LED will be driven<br>high asynchronously by either reset or<br>SWITCH[1]. After reset the LED will<br>remain on briefly, then act as the status light<br>for the LVDS loopback circuit 1. If the<br>loopback circuit is functioning properly, this<br>LED will flash. Otherwise, this LED will be<br>off. (This circuit is connected to SMA<br>connectors J3, J5, J6, J4, and test header<br>JP37). |

| LVDS_in2[0]  | 92            | LVDS Input      | LVDS positive input. Connect to<br>LVDS_out2[0] for loopback test.                                                                                                                                                                                                                                                                                                                                                          |

| LVDS_in2[1]  | 91            | LVDS Input      | LVDS negative input. Connect to<br>LVDS_out2[1] for loopback test.                                                                                                                                                                                                                                                                                                                                                          |

| LVDS_out2[0] | 97            | LVDS Output     | LVDS positive output. Connect to<br>LVDS_in2[0] for loopback test.                                                                                                                                                                                                                                                                                                                                                          |

| LVDS_out2[1] | 96            | LVDS Output     | LVDS negative output. Connect to<br>LVDS_in2[1] for loopback test.                                                                                                                                                                                                                                                                                                                                                          |

| LVDS_in1[0]  | 82            | LVDS            | LVDS positive input. Connect to<br>LVDS_out1[0] for loopback test.                                                                                                                                                                                                                                                                                                                                                          |

| LVDS_in1[1]  | 81            | Input           | LVDS negative input. Connect to<br>LVDS_out1[1] for loopback test.                                                                                                                                                                                                                                                                                                                                                          |

#### Table 1-2. Design Pin Description (Continued)

#### Setup and Self-Test

| Name         | Pin<br>Number | Pin Type        | Description                                                                                                                                                                                                                                |

|--------------|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LVDS_out1[0] | 88            | LVDS Input      | LVDS positive output. Connect to<br>LVDS_in1[0] for loopback test.                                                                                                                                                                         |

| LVDS_out1[1] | 87            | LVDS Output     | LVDS negative output. Connect to<br>LVDS_in1[1] for loopback test.                                                                                                                                                                         |

| SWITCH[1]    | 115           | LVTTL Input     | Asynchronously turns on all LEDs while<br>held. Sets LEDs[2:6] to <b>101010</b> for a short<br>period when released.                                                                                                                       |

| SWITCH[2]    | 114           | LVTTL Input     | Asynchronously turns off all LEDs while<br>held. Sets LEDs[2:6] to <b>010101</b> for a short<br>period when released.                                                                                                                      |

| SWITCH[3]    | 111           | LVTTL Input     | Sets LEDs[2:6] into a counting pattern. Any other switch will override the counting mode.                                                                                                                                                  |

| SWITCH[4]    | 110           | LVTTL Input     | Reset – asynchronous reset for all logic. Also<br>drives all LEDs high while held.                                                                                                                                                         |

| UartRX       | 3             | LVTTL Input     | Uart input signal. Note that the example<br>design does not actually contain a Uart. The<br>UartRX and UartTX signals are connected to<br>each other. This will echo any incoming<br>characters back to any terminal that is<br>connected. |

| UartTX       | 4             | LVTTL<br>Output | Uart output signal. See UartRX for more info.                                                                                                                                                                                              |

Table 1-2. Design Pin Description (Continued)

## **Hardware Description**

This chapter describes the components of the evaluation board. See Figure 1-1 on page 7 for a drawing of the evaluation board.

## **Axcelerator Evaluation Board Components**

The Axcelerator evaluation board consists of the following:

- · Wall mount power supply connector with switch and LED indicator

- Jumpers for I/O voltages of 1.5 V, 2.5 V or 3.3 V I/O on a per bank basis

- Multiple clock options

- · Four switches that provide input to the device

- · Eight LEDs driven by outputs from the device

- · Jumpers that allow disconnection of all external circuitry from the FPGA

- · Seven headers for easy access to device I/O signals

- Internal and external LVDS connections with loopback capability

For more information, refer to the following appendices:

- Appendix A "Board Connections" on page 59

- Appendix B "P160 Connections" on page 69

- Appendix C "Board Schematic" on page 73

#### **Power Supply**

The Axcelerator evaluation board has the following power supply requirements and features:

- Wall mount power supply

- 9 V, minimum 500 mA supply with 2.1 mm P5 type female connector (Note that the AX Starter Kit is supplied with a 9 V, 2 A supply as standard.)

- Digikey part number T413-P5P-ND for US

- Digikey Part Number T408-P5P-ND for Europe

- The power is controlled by an On/Off switch

- · LED D9 indicates the presence of a working wall mount supply

- LED D12 indicates the presence of a working 3.3 V source

Hardware Description

- LED D11 indicates the presence of a working 2.5 V source

- LED D13 indicates the presence of a working 1.5 V source

- JP1 JP8, one jumper per bank, can be used to select 1.5, 2.5, or 3.3 volts for the Device I/O Voltage, on a per bank basis

#### **Clock Circuits**

The evaluation board has multiple clock sources, which are described below.

#### **External Clock**

An external clock can be provided for the board using the SMA connector J7, which connects the external clock to pin 192 of the device. Pin 192 is a global HCLK input pin.

#### 40 MHz Oscillator

The 40 MHz oscillator is connected to J13, pin 19 (bank 5 header) on the board. J13, pin 20 connects to pin 76 of the device. Pin 76 is a global CLK input pin. If you want to use pin 76 for a different clock signal, disconnect the jumper across J13, pins 19/20.

#### **Multiplier Clock**

An ICS512 PLL clock multiplier is provided on the board. The clock multiplier uses Y1, a Pletronics 25.0 MHz crystal, as its external clock source. The multiplier output clock frequency is determined by the jumper settings of JP25, as described in Table 2-1 below.

| JP25 pins 1/2 | JP25 pins 3/4 | Clock Frequency |

|---------------|---------------|-----------------|

| Closed        | Closed        | 100 MHz         |

| Closed        | Open          | 133.33 MHz      |

| Open          | Closed        | 62.5 MHz        |

| Open          | Open          | 50 MHz          |

Table 2-1. JP25 Pins and Clock Frequency

The clock multiplier output is connected to J13, pin 21 (bank 5 header). J13, pin 22 connects to pin 77 of the device. Pin 77 is a global CLK input pin. If you want to use pin 77 for a different clock signal, disconnect the jumper across J13, pins 21/22.

#### **Clock Socket**

A clock socket, Y2, is provided on the board. The output of this socket is connected to J13, pin 17 (bank 5 header). J13, pin 18 connects to pin 70 of the device. Pin 70 is a global CLK input pin. If you want to use pin 70 for a different clock signal, disconnect the jumper across J13, pins 17/18.

#### **Manual Clock**

The manual clock button (SW6) lights D14, the pulse-generated LED, when activated, and generates a pulse. The manual clock is connected to J13, pin 15 (bank 5 header). J13, pin 16 connects to pin 71 of the device. Pin 71 is a global CLK input pin. If you want to use pin 71 for a different clock signal, disconnect the jumper across J13, pins 15/16.

### **LVDS** Connections

Both internal and external LVDS is available with loopback capability. Pads for SMA connectors are provided for external LVDS connections. Jumper JP37 allows for loopback of external LVDS connections, and Jumper JP36 allows for loopback of internal LVDS connections. The LVDS connections are detailed in Table 2-2.

| Source | Signal     | Jumper/Pin   | Device Connection |

|--------|------------|--------------|-------------------|

| SMA J3 | Receive P  | JP38 – Pin 3 | 82                |

| SMA J5 | Receive N  | JP38 – Pin 4 | 81                |

| SMA J6 | Transmit P | JP38 – Pin 1 | 88                |

| SMA J4 | Transmit N | JP38 – Pin 2 | 87                |

| Device | Receive P  | JP36 – Pin 1 | 92                |

| Device | Receive N  | JP36 – Pin 3 | 91                |

| Device | Transmit P | JP36 – Pin 2 | 97                |

| Device | Transmit N | JP36 – Pin 4 | 96                |

Table 2-2. LVDS Connections

Hardware Description

### LED Device Connections

Eight LEDs are connected to the device via jumpers. If the jumpers are in place, the device I/O can drive any of the LEDs. The LEDs change based on the following output:

- A 1 on the output of the device lights the LED.

- A 0 on the output of the device switches off the LED.

- An unprogrammed or tristated output may show a faintly lit LED.

Table 2-3 lists the LED/device connection.

Note: If you want to use the device I/O for other purposes, remove the jumpers.

| LED | Device Connection |

|-----|-------------------|

| D1  | 109               |

| D2  | 108               |

| D3  | 107               |

| D4  | 106               |

| D5  | 103               |

| D6  | 102               |

| D7  | 101               |

| D8  | 100               |

Table 2-3. LED Device Connection

### Switch Device Connections

Four switches are connected to the device via jumpers. If the jumpers are in place, the device I/O can be driven by the switches.

- Pressing the switch drives a 1 into the device. The 1 continues to drive while you hold the switch.

- Releasing the switch drives a 0 into the device.

Table 2-4 on page 17 lists the switch/device connections.

Note: If you want to use the device I/O for other purposes, remove the jumpers.

| Switch | Device Connection |

|--------|-------------------|

| SW1    | 115               |

| SW2    | 114               |

| SW3    | 111               |

| SW4    | 110               |

Table 2-4. Switch/Device Connection

## Headers

Seven headers are included on the board, allowing easy access to the AX250 I/Os. Table 2-5 lists the header connections.

| Pin | BANK 0/1           | BANK2              | BANK3              | BANK4              | BANK5              | BANK6              | BANK7              |

|-----|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| 1   | V <sub>CC1B0</sub> | 3.3 V              |

| 2   | 3.3 V              |

| 3   | V <sub>CCIB1</sub> | V <sub>CCIB2</sub> | V <sub>CCIB3</sub> | V <sub>CCIB4</sub> | V <sub>CCIB5</sub> | V <sub>CCIB6</sub> | V <sub>CCIB7</sub> |

| 4   | 1.5 V              |

| 5   | P199               | P154               | P129               | LED_1              | P54                | P27                | UART_SIN           |

| 6   | P198               | P153               | P128               | LED1               | P55                | P28                | UART_SOUT          |

| 7   | P197               | P152               | P127               | LED_2              | P56                | P29                | P5                 |

| 8   | P191               | P151               | P126               | LED2               | P57                | P30                | P6                 |

| 9   | P186               | P148               | P123               | LED_3              | P60                | P33                | P7                 |

| 10  | P185               | P147               | P122               | LED3               | P61                | P34                | P10                |

| 11  | P181               | P146               | P121               | LED_4              | P62                | P35                | P11                |

Table 2-5. Header Connections

#### Hardware Description

| Pin | BANK 0/1 | BANK2 | BANK3  | BANK4 | BANK5             | BANK6 | BANK7 |

|-----|----------|-------|--------|-------|-------------------|-------|-------|

| 12  | P180     | P145  | P120   | LED4  | P66               | P36   | P12   |

| 13  | P175     | P144  | P117   | LED_5 | P67               | P37   | P13   |

| 14  | P174     | P141  | P116   | LED5  | NC                | P40   | P16   |

| 15  | P171     | P140  | USER_1 | LED_6 | MANUAL_CLOC<br>K  | P41   | P17   |

| 16  | P170     | P139  | USER1  | LED6  | MANUAL_CLK_I<br>N | P42   | P18   |

| 17  | P166     | P138  | USER_2 | LED_7 | CLK_SOCKET        | P43   | P19   |

| 18  | P165     | P137  | USER2  | LED7  | CLK_SOCKET_I      | P44   | P22   |

| 19  | P162     | P136  | USER_3 | LED_8 | OSC_CLK           | P47   | P23   |

| 20  | P161     | P135  | USER3  | LED8  | OSC_CLK_IN        | P48   | P24   |

| 21  | P160     | P134  | USER_4 | NC    | MULT_CLK          | P49   | P25   |

| 22  | P159     | P133  | USER4  | NC    | MULT_CLK_IN       | P50   | NC    |

| 23  | GND      | GND   | GND    | GND   | GND               | GND   | GND   |

| 24  | GND      | GND   | GND    | GND   | GND               | GND   | GND   |

Table 2-5. Header Connections (Continued)

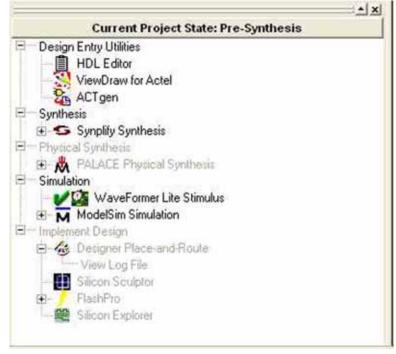

This tutorial illustrates a basic Verilog design for an Axcelerator evaluation board. The design targets the Actel Axcelerator family. This tutorial contains the following nine high-level steps:

- "Step 1 Create a New Project"

- "Step 2 Add ACTgen Components"

- "Step 3 Perform a Pre-Synthesis Simulation"

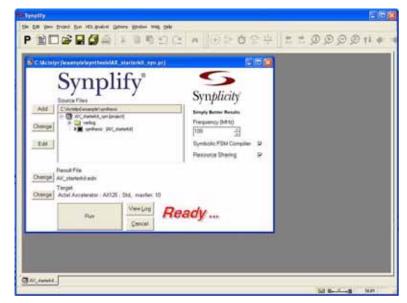

- "Step 4 Synthesize the Design in Synplify®"

- "Step 5 Perform a Post-Synthesis Simulation"

- "Step 6 Implement the Design Using Designer"

- "Step 7 Perform a Timing Simulation with Back-Annotated Timing"

- "Step 8 Generate the Programming File"

- "Step 9 Program the Device"

In this tutorial, you will create a self-checking serial loopback system operating at 40 MHz. The AX device will transmit and receive data at 80 Megabits per second using its DDR functionality. A 10-bit test pattern (0101110011) will transmit and receive using the AX device's LVDS I/Os.

## Step 1 – Create a New Project

In this step you will use the Libero IDE HDL editor to enter the Actel Verilog design.

#### To create the Verilog project:

1. Start Libero IDE by double-clicking the Actel Libero IDE icon on your desktop.

2. From the File menu, choose *New Project*. The New Project Wizard dialog box is displayed, as shown in Figure 3-1.

| new Libero p | ect Wizard<br>roject.<br>xxample |            |

|--------------|----------------------------------|------------|

| name: [e     | mample                           |            |

|              |                                  |            |

| location: 0  | 2VActelprj\example               | <br>Browse |

| pe: G        | Verilog<br>VHDL                  | Help       |

|              | pe: G                            |            |

Figure 3-1. Project Wizard Welcome

- 3. Type *example* in the Project name field.

- 4. In the Project location field, click *Browse* to navigate to C:\Actelprj.

- 5. Type *example* in the Project location field after C:\Actelprj.

- 6. Select the *Verilog* radio button in the HDL type field.

- 7. Click Next.

Step 1 – Create a New Project

8. Select the Axcelerator family, AX250 die, and 208PQFP package. See Figure 3-2.

| Select the    | lamily, die and package of your ne   | w project.                                   |

|---------------|--------------------------------------|----------------------------------------------|

| Start         | Family:                              |                                              |

| Select Device | Axcelerator 💌                        | Help                                         |

| Select Tools  | Die:                                 | Package:                                     |

| Add Files     | AX125                                | 208 PQFP                                     |

| Finish        | AX250<br>RTAX250S<br>AX500<br>AX1000 | 208 CQFP<br>256 FBGA<br>352 CQFP<br>484 FBGA |

| 1             | RTAX1000S<br>AX2000<br>RTAX2000S     |                                              |

Figure 3-2. Family, Die, and Package

9. Click Finish.

The software creates the project example and opens it in the Libero IDE.

10. From the File menu, choose New.

The New dialog box opens, as shown in Figure 3-3.

| ew                                                                                                                                     |        |

|----------------------------------------------------------------------------------------------------------------------------------------|--------|

| File Type:                                                                                                                             | OK     |

| Schematic<br>ACT gen macro                                                                                                             | Cancel |

| Verilog Header File<br>Verilog Header File<br>Stimulus<br>Stimulus HDL File<br>SDC File (sdc)<br>Physical Design Constraint File (pdc) | Help   |

| Name:                                                                                                                                  |        |

Figure 3-3. New Dialog Box

- 11. Select Verilog Module in the File Type field.

- 12. Type *DDR\_loopback* in the Name field.

- 13. Click OK.

The HDL Editor opens.

- 14. Enter the DDR\_loopback file, described in Appendix A ("Board Connections" on page 59). If the document is open in an electronic form, cut and paste it from this document.

- 15. From the File menu, choose Save.

Step 1 – Create a New Project

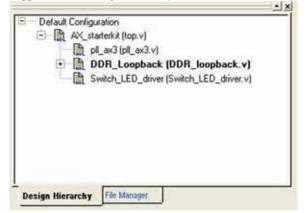

The design file **DDR\_loopback** appears on the Design Hierarchy tabbed page in Libero IDE. The file name **DDR\_loopback** is listed under HDL files on the File Manager tabbed page in the Libero IDE, as shown in Figure 3-4 and Figure 3-5.

| and the second se | Loopback (DDR_loopback.v)<br>dr_transmitter (DDR_loopback.v) |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| taot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                              |

Figure 3-4. Design Hierarchy Tab

| Project Design<br>Block Sym |              |  |

|-----------------------------|--------------|--|

| Schematic                   |              |  |

| Package F                   | iles         |  |

| - HDL Files                 |              |  |

| DD                          | R_loopback.v |  |

| ACT gen M                   | acros        |  |

| • Implementa                | ation Files  |  |

| Stimulus Fi                 | les          |  |

|                             |              |  |

|                             |              |  |

|                             |              |  |

Figure 3-5. File Manager Tab

- 16. Click the *File Manager* tab.

- 17. Right-click on *DDR\_loopback.v* and select *check HDL*.

This checks the syntax of the **DDR\_loopback.v** file. Before moving to the next section, check the code for errors and make modifications if necessary.

18. Repeat steps 8-13 for *Switch\_LED\_driver.v* and *top.v* files.

## Step 2 – Add ACTgen Components

In this step, you learn how to add ACTgen components.

#### To add ACTgen components:

1. Click on the ACTgen icon in the Design Flow window.

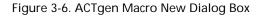

The New dialog box opens, as shown in Figure 3-6. The ACTgen macro file type is selected.

| ile Type:                                                                                                                         | OK     |

|-----------------------------------------------------------------------------------------------------------------------------------|--------|

| Schematic<br>ACT gen macro                                                                                                        | Cancel |

| Verilog Module<br>Verilog Header File<br>Stimulus<br>Stimulus HDL File<br>SDC File (sdc)<br>Physical Design Constraint File (pdc) | Help   |

| Vame:                                                                                                                             |        |

2. Enter *pll\_ax3* in the Name field and click *OK*.

The ACTgen GUI opens.

3. Select *PLL* macros in the ACTgen GUI, as shown in Figure 3-7.

Figure 3-7. PLL Macros

4. Select the *Both Outputs* option in the Variety View window.

The ACTgen Macro Builder – PLL dialog box opens. Enter the following values, as shown in Figure 3-8 on page 26:

- REF Clock: 40 MHz

- CLK1: 40 MHz

- CLK2: 80 MHz

| REF Clash     Frequency (Ms) | 412000                                  | Freedback<br>AF bolomed                                                                                         |  |

|------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|

| Dela Sel                     | 4 then (100 ±                           | Cland                                                                                                           |  |

| best .                       | P Dynamic<br>P Hardward (107 Data Logic | Canceding                                                                                                       |  |

|                              | C Enerali/D                             | 4 Ma                                                                                                            |  |

| The second                   | and the second second                   |                                                                                                                 |  |

| P (DA1                       | Frequency (HPS)                         | pet outer                                                                                                       |  |

| Chek Dar                     | C R Reded of                            | Toustle :                                                                                                       |  |

|                              |                                         |                                                                                                                 |  |

| F 0.62                       | Tespeno 2011                            | 5mi 0000                                                                                                        |  |

| - Del Da                     |                                         | pin one                                                                                                         |  |

| P. carter                    | W Rodet                                 | Roadle                                                                                                          |  |

|                              |                                         |                                                                                                                 |  |

|                              | n I Base I                              | me l                                                                                                            |  |

|                              |                                         | the second se |  |

Figure 3-8. ACTgen Macro Builder - PLL

5. Click the *Save* button.

The Save As dialog box opens.

6. Verify that all the information is correct and click *Save*.

The pll\_ax3 file appears in the Design Hierarchy window, as shown in Figure 3-9.

Figure 3-9. Design Hierarchy, pll\_ax3

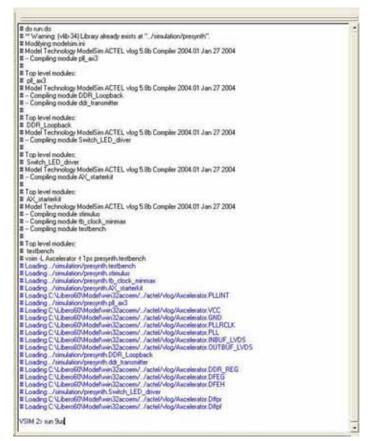

## Step 3 – Perform a Pre-Synthesis Simulation

The next step is to simulate the RTL description of the design. First, you will use SynaptiCAD WaveFormer Lite<sup>TM</sup> AE to create a stimulus for the design, and then you will generate a test bench for the design.

#### **Creating a Stimulus Using WaveFormer Lite**

WaveFormer Lite generates VHDL test benches from drawn waveforms. Listed below are the three basic steps for creating test benches using WaveFormer Lite and the Actel Libero IDE software:

- Importing Signal Information

- · Drawing and Copying Waveforms

- Exporting the Test Bench

#### **Importing Signal Information**

Follow the steps below to launch WaveFormer Lite and import the signal information into it.

#### To launch WaveFormer Lite and import signal information:

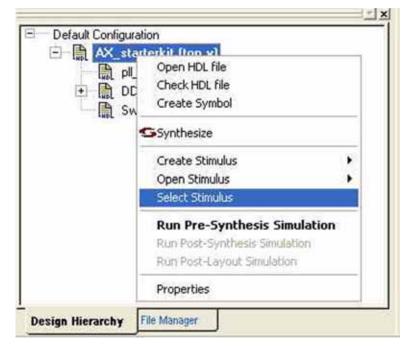

1. Before you start WaveFormer Lite, make sure that the AX\_starterkit block is at the top level (it will be in a bold font style on the Design Hierarchy tabbed page). If the AX\_starterkit is not at the top level, right-click the file and select set as root.

2. Click the *WaveFormer Lite* icon in the Libero IDE, or right-click the *AX\_starterkit* file on the Design Hierarchy tabbed page and select *Create Stimulus*.

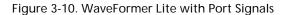

WaveFormer Lite launches and the port signals appear in the diagram window, as shown in Figure 3-10.

| Diagram - AX_sta                           | rterkit_tbenc            | h.btim |         |       |     |         |   |        |

|--------------------------------------------|--------------------------|--------|---------|-------|-----|---------|---|--------|

| Add Signal Add Bus<br>Add Clock Add Spacer | Delay Setup<br>Hold Text |        | HEH LOW | TRI V |     | WHI WLO | 聖 | 9+9    |

| 222.0ns 222.0ns                            | Ons                      | 50ns   |         | 100ns | 1.1 | 150ns   |   | (200ns |

| LED_put[7:0]                               |                          |        |         |       |     |         |   | ^      |

| SWITCH[3:0]                                |                          |        |         |       |     |         |   | 1      |

| LVDS_in1[1:0]                              |                          |        |         |       |     |         |   |        |

| EVDS_out1[1:0]                             |                          |        |         |       |     |         |   | i.     |

| CLK_in                                     |                          |        |         |       |     |         |   |        |

| LVDS_in2[1:0]                              |                          |        |         |       |     |         |   | 8      |

| LVDS_put2[1.0]                             |                          |        |         |       |     |         |   |        |

| UartRX                                     |                          |        |         |       |     |         |   | 1      |

| Uartix                                     |                          |        |         |       |     |         |   |        |

|                                            |                          |        |         |       |     |         |   |        |

|                                            |                          |        |         |       |     |         |   |        |

|                                            |                          |        |         |       |     |         |   |        |

| c als                                      | c                        |        |         |       |     |         |   | ×      |

As shown in Figure 3-10, the AX\_starterkit design contains the following signals:

- LED\_out output signals

- SWITCH input signals

- LVDS\_in1 input signals

- LVDS\_out1 output signals

- CLK\_in input signals

- LVDS\_in2 input signals

- LVDS\_out2 output signals

- UartRX input signals

- UartTX output signals

#### **Drawing Waveforms**

The state buttons are the buttons labeled with pictures of waveforms: HIGH, LOW, TRIstate, VALid, INValid, WHI (weak high), and WLO (weak low), as shown in Figure 3-11.

Figure 3-11. State Buttons

When a state button is activated, it is pushed in and colored red. The active state is the type of waveform that is drawn next. Click a state button to activate it.

The state buttons automatically toggle between the two most recently activated states. The state with the small red '1' above the name will be the toggle state. The initially activated state is HIGH and the initial toggle state is LOW in Figure 3-11.

Signal edges are automatically aligned to the closest edge grid when you draw signals using the mouse. Control the edge grid with the **Options > Grid Setting** menu items.

#### To draw a waveform:

- 1. Select the *High* state and place the mouse cursor inside the diagram window at the same vertical row as the signal name.

- 2. Click with the left mouse button.

This draws a waveform from the end of the signal to the mouse cursor. The red state button on the button bar determines the type of waveform drawn. The cursor shape also mirrors the red state button.

3. Move the mouse to the right and click again to draw another segment.

#### **Copying Waveforms**

You can copy and paste sections of waveforms onto (overwrite) or into (insert) any signal in the diagram.

#### To copy and paste waveform sections:

1. Select the names of the required signals. If you do not select a signal, the *Block Copy* command selects all the signals in the diagram.

2. From the Edit menu, select *Block Copy Waveforms*. This opens the **Block Copy Waveforms** dialog box with the selected signals displayed in the **Change Waveform Destination** list box, as shown in Figure 3-12.

| Rat:                                               | 13 | ns | 🕫 In                                                   | sert      |

|----------------------------------------------------|----|----|--------------------------------------------------------|-----------|

| End:                                               | 0  | ns | Co                                                     | renvirite |

| Nace At:                                           | 0  | ns | # of Copi                                              | es: 1     |

| LVDS_ou<br>CLK_in<br>LVDS_ini<br>LVDS_ou<br>UartRX | 2  |    | LVDS_out1<br>CLK_in<br>LVD5_in2<br>LVD5_out2<br>UartRX |           |

| UartTX                                             |    |    | UartTX                                                 |           |

Figure 3-12. Block Copy Waveform Dialog Box

- 3. In the *Block Copy Waveforms* dialog box, enter the values that define copy and paste (*Start, End,* and *Place At*).

- 4. Select either *Time* or *Clock Cycles* for the basic units of the dialog.

- 5. When entering values, remember the following:

- When copying only signals (no clocks), time is the default base unit of the dialog.

- When copying part of a clock, it is best to choose **clock cycles** as the base unit; choose the copied clock as the reference clock.

- If time is selected when copying clocks, the End time minus Start time must equal an integral number of clock periods, and the Place At time must be at the same clock period offset as the Start time.

- Start and End define the times of the block copy.

- Place At is the time at which the block will be pasted.

#### Step 3 – Perform a Pre-Synthesis Simulation

- The **Insert** and **Overwrite** radio buttons determine whether the paste block is inserted into the existing waveforms or overwrites those waveforms.

- The list box at the bottom of the dialog determines which signal the copied waveforms will be pasted into.

#### To change this mapping:

• Select a line in the list box.

This places the destination signal in the drop-down list box on top of the list box.

• Select another signal from the drop-down list box.

Each destination signal can be used only once per copy.

6. Click OK to complete the copy and paste operation.

#### **Creating Clocks**

The signal CLK\_in is a clock signal. Instead of drawing the entire clock waveform, Waveformer Lite allows you to create the clock signals with the GUI.

#### To create the CLK\_in with the GUI:

- 1. Left-click the CLK\_in signal name once to select it.

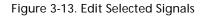

- 2. Right-click the *CLK\_in* signal name.

A shortcut menu appears.

- Diagram AX\_starterkit\_thench.htlm\* Add But Delay Setal Seals 9-91 0.000ps 0.000ps (films (100na (15049 (200hia) \_\_\_\_\_\_250mi (300ns SWITCH[4 1] LVDS\_in1[1:0] Edit Selected Signals). LVDS Save As

- 3. Click Signal(s) <-> Clock(s) (see Figure 3-13). A clock signal appears.

4. Double-click (left mouse button) the *CLK\_in* signal.

Step 3 – Perform a Pre-Synthesis Simulation

| Signal Properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2 🛛               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Name:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Active Low        |

| Sinclate Occa Analog Props                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Grid Lines        |

| C Drive C Sinclote C Watch<br>Boolean Equation: ex. (SIG1 and SIG2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   |

| ſ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <u>ile</u>        |

| Close Undedlad - Edgefiere                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1 000 y           |

| Clock Properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

| ChickEnable Net Used - Ad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | vincéd Reaster;   |