# Implementing Multi-Port Memories in ProASIC<sup>PLUS</sup> Devices

# **Table of Contents**

| Introduction                     |

|----------------------------------|

| Dual-Port Memory                 |

| Quad-Port Memory                 |

| Implementing Multi-Port Memories |

| Read Ports: Dual-Port Memory     |

| Read Ports: Quad-Port Memory     |

| Write Ports                      |

| Timing Diagrams                  |

| Design Considerations            |

| Utilization                      |

| Conclusion                       |

| Related Documents                |

| Appendix: Design Example         |

| List of Changes                  |

# Introduction

This application note describes a user-configurable VHDL wrapper for implementing dual-port and quad-port memory structures using a small number of programmable logic tiles and the embedded memory blocks in Microsemi ProASIC<sup>PLUS®</sup> field programmable gate array (FPGA) devices.

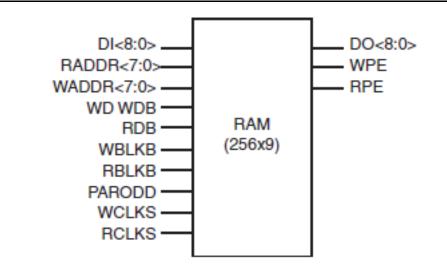

The ProASIC<sup>PLUS</sup> device architecture contains embedded SRAM cells that can be configured as static memory blocks with independent read and write ports. Each basic memory block has a size of 256 words by 9 bits with a single data port interface. For additional details on embedded memory blocks in ProASIC<sup>PLUS</sup> devices, refer to *ProASICPLUS Flash Family FPGAs Datasheet* or *AC281: ProASICPLUS RAM-FIFO Blocks Application Note*.

Figure 1 shows a block diagram of the basic memory block.

### Figure 1 • Basic Embedded SRAM Memory Block Structure

The embedded memory blocks in ProASIC<sup>PLUS</sup> devices can be used to implement multi-port memories with the addition of some simple multiplex logic and an extra clock operating at double the read and write clock frequency.

## **Basics of Multi-Port Memories**

This application note discusses two types of multi-port memories—dual-port and quad-port. In both configurations, two data access ports (data port A and data port B) are available for simultaneous read and write operations into the ProASIC<sup>PLUS</sup> embedded SRAM blocks. Each data port has its own data bus, address bus, read enable, and write enable signals. The basic principle of implementing multi-port memories in ProASIC<sup>PLUS</sup> devices involve the use of an additional clock operating at double the read and write frequency to access the memory space through some multiplex logic and arbitrate between the data access ports. The overall bandwidth of the memory (bit or bits) remains the same, and the only difference between the single and the multi-port memory is the read/write frequency versus data width-trade off.

Although more than one data access port is now available, they share the same memory space. Simultaneous read/write cycles to the same memory address result in reading the pre-existing memory contents followed by the memory being updated with the new data at the end of the clock cycle.

### **Dual-Port Memory**

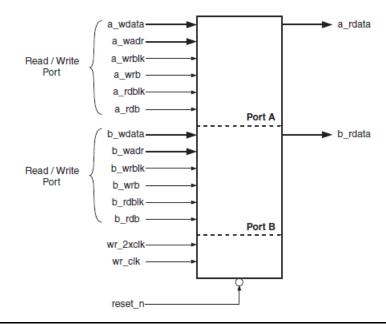

The dual-port memory configuration consists of two data access ports (two read/write ports) sharing a single clock domain (wr\_clk). The write address bus from each data access port (a\_wadr and b\_wadr) is used for both read and write operations. The read enable (a\_rdblk, a\_rdb, b\_rdblk, and b\_rdb) and write enable (a\_wrblk, a\_wrb, b\_wrblk, and b\_wrb) signals are used to select between either read or write operation for each data access port. Figure 2 on page 3 shows the corresponding ports of a dual-port memory block.

## **Quad-Port Memory**

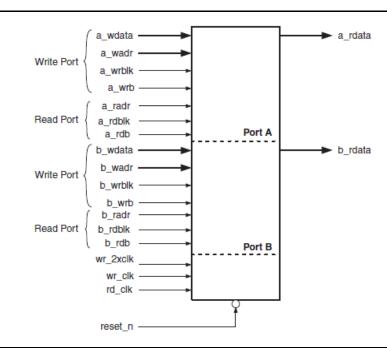

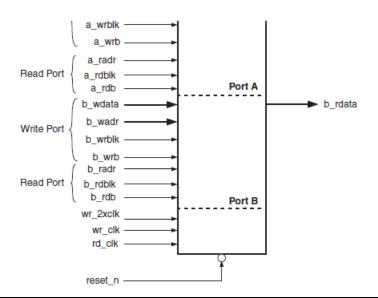

The quad-port memory configuration consists of two data access ports, each with a separate write port and read port, clocked by separate write (wr\_clk), and read (rd\_clk) clocks. For each data access port, there are separate address busses used to perform read (a\_radr and b\_radr) and write (a\_wadr and b\_wadr) operations. The read enable (a\_rdblk, a\_rdb, b\_rdblk, and b\_rdb) and write enable (a\_wrblk, a\_wrb, b\_wrblk, and b\_wrb) signals are used to activate the read and write operations for each data access port.

Figure 2 shows the corresponding ports of a dual-port memory block.

Figure 2 • Dual-Port Memory Block Interface Signals

Figure 3 shows the corresponding ports of a quad-port memory block.

### Figure 3 • Quad-Port Memory Block Interface Signals

Table 1 summarizes the interface signals of the memory block.

| Signal   | Bits     | Input/Output | Description                                     |

|----------|----------|--------------|-------------------------------------------------|

| a_wdata  | variable | Input        | Write data bus                                  |

| a_wadr   | 8        | Input        | Write/dual-port memory address bus              |

| a_wren   | 1        | Input        | Active high data enable                         |

| a_rdata  | variable | Output       | Output data bus                                 |

| a_radr   | 8        | Input        | Output address bus (quad-port memory mode only) |

| a_rden   | 1        | Input        | Output register enable A                        |

| b_wdata  | variable | Input        | Write data bus                                  |

| b_wadr   | 8        | Input        | Write / dual-port memory address bus            |

| b_wren   | 1        | Input        | Active high data enable                         |

| b_rdata  | variable | Output       | Output data bus                                 |

| b_radr   | 8        | Input        | Output address bus (quad-port memory mode only) |

| b_rden   | 1        | Input        | Output register enable B                        |

| wr_2xclk | 1        | Input        | 2x write clock                                  |

| wr_clk   | 1        | Input        | Write port data clock / multiplexer select      |

| rd_2xclk | 1        | Input        | 2x read clock (quad-port memory mode only)      |

| rd_clk   | 1        | Input        | Read data clock (quad-port memory mode only)    |

| reset_n  | 1        | Input        | Reset signal (active low)                       |

## **Implementing Multi-Port Memories**

In the referenced example ("Appendix: Design Example" on page 10), the multi-port memory wrapper can be implemented in two configurations as described above: dual-port memory (PMODE=0) and quad-port memory (PMODE = 1). The depth of the implemented multi-port memories is limited to a single memory block (that is 256 words), but the width is variable up to 72 bits. The ProASIC<sup>PLUS</sup> RAM256X9SA macro is used as the basic memory block for this wrapper.

Since implementation of multi-port memories relies on the embedded memory block being clocked at twice the data clock rate, a double frequency clock needs to be generated. The original data clock input (wr\_clk) is easily doubled in frequency to generate the required wr\_2xclk signal using the PLLs in ProASIC<sup>PLUS</sup> architecture. For more information on how to generate a PLL for ProASIC<sup>PLUS</sup> devices, refer to *Microsemi SmartGen, FlashROM, ASB, and Flash Memory System Builder User Guide* or *AC306: Using ProASICPLUS Clock Conditioning Circuits Application Note.*

Table 2 describes the configurable parameters for the reference design in the "Appendix: Design Example" on page 10.

| Parameter | Value              | Description                                            |

|-----------|--------------------|--------------------------------------------------------|

| PMODE     | 0 (default)        | Dual-port memory configuration                         |

|           | 1                  | Quad-port memory configuration                         |

| PIPE      | 0 (default)        | Inputs not registered, just multiplex logic for inputs |

|           | 1                  | Register inputs, then multiplex inputs to memory       |

| OREG      | 0 (default)        | Transparent output mode                                |

|           | 1                  | Registered output mode                                 |

| WIDTH     | 1:72 (default = 9) | Number of data + parity bits                           |

Table 2 • Configurable Parameters for Design Example in Appendix

### **Read Ports: Dual-Port Memory**

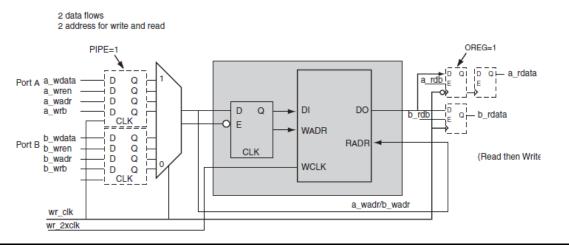

A block diagram of the dual-port memory implementation is shown in Figure 4.

Figure 4 • Dual-Port Memory Implementation

In this configuration, the write addresses and write clock are used to read from the memory. The read address inputs and read clock remain unused in the code. If OREG = 0, the data outputs propagate directly to both of the data output ports; otherwise, when OREG = 1, the output is pipelined with the rising-edge of wr\_clk. Data for the Read/Write Port A is registered on the falling-edge of wr\_clk and then re-timed to the next rising-edge, while data for Read/Write Port B is registered on the rising-edge of wr\_clk. This resynchronizes the data on Port A and Port B so that the apparent operation of the memory is to read both ports simultaneously. The memory read operation supported by this wrapper is asynchronous. The read enable inputs are used as inputs to enable the output registers.

## **Read Ports: Quad-Port Memory**

A block diagram of the quad-port memory implementation is shown in Figure 5.

#### Figure 5 • Quad-Port Memory Implementation

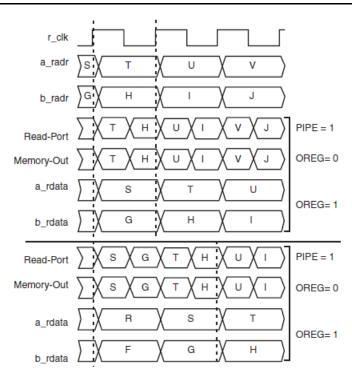

If PIPE is set to 1, the address and enable inputs for both read ports are registered with the rising edge of the read clock rd\_clk. Then, the read address and read enable inputs for Port A and Port B are multiplexed to the memory and settle, while the rd\_clk signal is high and low, respectively. If PIPE is set to 0, the read address and enables are not registered and the read address and read enable inputs for Port A and Port B are simply multiplexed to access the ProASIC<sup>PLUS</sup> memory.

If OREG = 0, the data outputs propagate directly to the data output ports; otherwise when OREG = 1, the output is resynchronized with the rising-edge of rd\_clk. Read data for Read Port A is registered on the falling-edge of rd\_clk and then re-timed to the next rising-edge, and read data for Read Port B is registered on the rising-edge of rd\_clk. This resynchronizes the data on Port A and Port B so that the apparent operation of the memory is to read both ports simultaneously. The memory read operation supported by this wrapper is asynchronous. The read enable inputs are used as inputs to enable the output registers.

### **Write Ports**

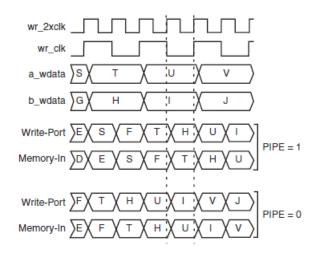

The Write Port implementation for both dual-port and quad-port memory is the same. Data, address, and enables for both write ports are optionally registered with the rising edge of wr\_clk when PIPE = 1. Data, address, and enable signals for Port A and Port B are multiplexed to the memory and settle while wr\_clk signal is high and low respectively. Then data is written into the memory on the next rising edge of wr\_2xclk (next falling or rising edge of wr\_clk).

## **Timing Diagrams**

Figure 6 and Figure 7 shows the relationships of the signals during Write and Read Cycles for both dual-port and quad-port memories.

Figure 6 • ProASICPLUS Multi-Port memory Implementation Write Cycle

Figure 7 • ProASIC<sup>PLUS</sup> Multi-Port memory Implementation Read Cycle

## **Design Considerations**

The implementation of both dual-port memory and quad-port memory involves doubling the clock frequency at which data is clocked into ProASIC<sup>PLUS</sup> embedded memory and the use of multiplex logic to arbitrate between Port A and Port B. The simplest way to implement the doubled frequency is to make use of the on-chip PLL, with the exact configuration generated using ACTgen Macro Builder.

## Utilization

Using the reference design example in the "Appendix: Design Example" on page 10, the following tables quantify the additional logic overhead introduced by the necessary gates, flip-flops, and PLL used in both dual-port and quad-port memory configurations in un-registered versus registered inputs and outputs configuration.

The limiting portion of the design is the use of a doubled-frequency clock to a read/write into memory. The maximum PLL output frequency is 180 MHz, as listed on *ProASICPLUS Flash Family FPGAs Datasheet*. Therefore; if PLL is used to generate the doubled-frequency clock, the operation of the wrapper code is at a limit of 90 MHz read/write. To achieve faster performance, the double-frequency clock can be generated off chip.

If the configuration has the outputs registered (OREG = 1), this generates opposite edge flip-flops that is part of the critical path of the design.

Dual-Port Memory with Unregistered Inputs and Outputs.

| Data Width     | 9 Bits | 18 Bits | 36 Bits | 72 Bits |

|----------------|--------|---------|---------|---------|

| Core Cells     | 19     | 28      | 46      | 82      |

| RAM/FIFO Cells | 1      | 2       | 4       | 8       |

| PLLs           | 1      | 1       | 1       | 1       |

### Table 3 • Designer Resource Utilization Report (PMODE = 0, PIPE = 0, OREG = 0)

Dual-Port Memory with Registered Inputs and Outputs.

### Table 4 • Designer Resource Utilization Report (PMODE = 0, PIPE = 1, OREG = 1)

| Data Width     | 9 Bits | 18 Bits | 36 Bits | 72 Bits |

|----------------|--------|---------|---------|---------|

| Core Cells     | 114    | 195     | 356     | 680     |

| RAM/FIFO Cells | 1      | 2       | 4       | 8       |

| PLLs           | 1      | 1       | 1       | 1       |

Quad-Port Memory with Unregistered Inputs and Outputs.

#### Table 5 • Designer Resource Utilization Report (PMODE = 1, PIPE = 0, OREG = 0)

| Data Width     | 9 Bits | 18 Bits | 36 Bits | 72 Bits |

|----------------|--------|---------|---------|---------|

| Core Cells     | 27     | 36      | 54      | 90      |

| RAM/FIFO Cells | 1      | 2       | 4       | 8       |

| PLLs           | 1      | 1       | 1       | 1       |

Quad-Port Memory with Registered Inputs and Outputs.

### Table 6 • Designer Resource Utilization Report (PMODE = 1, PIPE = 1, OREG = 1)

| Data Width     | 9 Bits | 18 Bits | 36 Bits | 72 Bits |

|----------------|--------|---------|---------|---------|

| Core Cells     | 142    | 223     | 384     | 708     |

| RAM/FIFO Cells | 1      | 2       | 4       | 8       |

| PLLs           | 1      | 1       | 1       | 1       |

Notice the utilization increases significantly from the unregistered inputs and outputs to the registered configuration. This is due to the additional flip-flops necessary to generate the registered inputs and outputs for each bit of the data and address busses, as well as the enable signals. Also, the utilization shows a slight increase from the dual-port to quad-port memory configuration.

## Conclusion

Implementation of multi-port memories using a wrapper source code to interface the basic ProASIC<sup>PLUS</sup> memory block is straightforward and intuitive. Although, implementation of both dual-port and quad-port memories requires additional logic overhead, including extra multiplexers, and flip-flops, still proves useful in certain designs.

While the particular reference design included in the "Appendix: Design Example" on page 10 does not account for parity, parity input and output signals can be easily implemented in the multi-port memory wrapper source code. First, make use of the parity checking/generating capabilities built-in to the ProASIC<sup>PLUS</sup> memory blocks, and instantiate the desired memory macro in place of the RAM256x9SA used in the example. Then, follow the basic principle of multiplexing Port A and Port B parity signals at rising and falling edges of the clock signal.

# **Related Documents**

For more information, see the following documents:

- ProASICPLUS Flash Family FPGAs Datasheet

- AC281: ProASICPLUS RAM-FIFO Blocks Application Note

- AC306: Using ProASICPLUS Clock Conditioning Circuits Application Note

- Microsemi SmartGen, FlashROM, ASB, and Flash Memory System Builder User Guide

## **Appendix: Design Example**

This design example implements a variable width dual-port or quad-port memory (up to 72 bits wide), based on the 256  $\times$  9 memory blocks available in Microsemi ProASIC<sup>PLUS</sup> devices. For deeper memories, the user must gang these blocks together and modify this design example.

A sample instantiation of the multi-port memory wrapper, which may be cut and pasted into the higherlevel VHDL code are as follows:

```

-- QPM0: mpm apa

-- GENERIC MAP (PMODE => 0, PIPE = 0, OREG = 0, WIDTH = 9);

___

-- PORT MAP (reset n => <your reset>,

-- wr 2xclk => <2x write clock>,

-- wr clk => <write port data/enable clock>,

-- a wrblk => <active low block enable for write>,

-- a wrb => <active low data enable for write>,

-- a wadr => <write/dpm address bus (8-bits)>,

-- a wdata => <write data bus (variable width)>,

-- b wrblk => <active low block enable for write>,

-- b wrb => <active low data enable for write>,

-- b wadr => <write/dpm address bus (8-bits)>,

-- b wdata => <write data bus (variable width)>,

-- rd clk => <read data clock (QPM mode)>,

-- a rdblk => <output register enable 1>,

-- a rdb => <output register enable 2>,

-- a radr => <output address bus 8-bits (QPM mode)>,

-- a rdata => <output data bus (variable width)>,

-- b rdblk => <output register enable 1>,

-- b rdb => <output register enable 2>,

-- b radr => <output address bus 8-bits (QPM mode)>,

-- b rdata => <output data bus (variable width)>);

The multi-port memory implementation source code are as follows:

Note: The source code can also be obtained from Microsemi Technical Support or from your local FAE.

_____

--

-- Copyright 2002 Microsemi Corporation

_____

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.std logic unsigned.all;

-- depending on the tools suite used, the APA library

-- may need to be referenced for VITAL simulation models.

--library apa;

--use apa.all;

```

```

-- NOTE: Integer types are used for all GENERIC declarations

-- in order to include synopsys support.

entity mpm apa is

generic (PMODE : INTEGER range 0 to 1 := 0; -- DPM, QPM

PIPE : INTEGER range 0 to 1 := 0; -- M, R

OREG : INTEGER range 0 to 1 := 0; -- M, R

WIDTH : INTEGER range 1 to 72 := 9); -- 1:72

port( reset n : in std logic; -- active low

wr 2xclk : in std logic;

wr_clk : in std_logic;

a wrblkb : in std logic;

a wrb : in std logic;

a_wadr : in std_logic_vector(7 downto 0);

a_wdata : in std_logic_vector(WIDTH - 1 downto 0);

b wrblkb : in std logic;

b wrb : in std logic;

b_wadr : in std_logic_vector(7 downto 0);

b wdata : in std logic vector(WIDTH - 1 downto 0);

rd_clk : in std_logic;

a rdblkb : in std logic;

a rdb : in std logic;

a_radr : in std_logic_vector(7 downto 0);

a_rdata : out std_logic_vector(WIDTH - 1 downto 0);

b rdblkb : in std logic;

b rdb : in std logic;

b radr : in std logic vector(7 downto 0);

b_rdata : out std_logic_vector(WIDTH - 1 downto 0));

end mpm apa;

architecture RTL of mpm apa is

-- APA 256x9 RAM with parity checking (parity not used)

component RAM256x9SA

port(

DO8 :out STD ULOGIC;

DO7 :out STD_ULOGIC;

DO6 :out STD ULOGIC;

DO5 :out STD ULOGIC;

DO4 :out STD ULOGIC;

DO3 :out STD ULOGIC;

DO2 :out STD ULOGIC;

DO1 :out STD_ULOGIC;

DO0 :out STD ULOGIC;

```

```

WPE :out STD ULOGIC;

RPE :out STD ULOGIC;

DOS :out STD_ULOGIC;

WADDR7 :in STD ULOGIC;

WADDR6 :in STD ULOGIC;

WADDR5 :in STD ULOGIC;

WADDR4 :in STD ULOGIC;

WADDR3 :in STD ULOGIC;

WADDR2 :in STD ULOGIC;

WADDR1 :in STD ULOGIC;

WADDR0 :in STD ULOGIC;

RADDR7 :in STD ULOGIC;

RADDR6 :in STD ULOGIC;

RADDR5 :in STD_ULOGIC;

RADDR4 :in STD ULOGIC;

RADDR3 :in STD ULOGIC;

RADDR2 :in STD ULOGIC;

RADDR1 :in STD ULOGIC;

RADDR0 :in STD ULOGIC;

WCLKS :in STD ULOGIC;

DI8 :in STD ULOGIC;

DI7 :in STD ULOGIC;

DI6 :in STD ULOGIC;

DI5 :in STD_ULOGIC;

DI4 :in STD_ULOGIC;

DI3 :in STD ULOGIC;

DI2 :in STD ULOGIC;

DI1 :in STD ULOGIC;

DIO :in STD ULOGIC;

WRB :in STD ULOGIC;

RDB :in STD ULOGIC;

WBLKB :in STD ULOGIC;

RBLKB :in STD ULOGIC;

PARODD :in STD ULOGIC;

DIS :in STD ULOGIC);

end component;

SIGNAL wrblk a : std logic;

SIGNAL wrb a : std logic;

SIGNAL wadr_a : std_logic_vector(7 downto 0);

SIGNAL wdata_a : std_logic_vector(WIDTH - 1 downto 0);

SIGNAL wrblk_b : std_logic;

SIGNAL wrb b : std logic;

SIGNAL wadr b : std logic vector(7 downto 0);

SIGNAL wdata b : std logic vector(WIDTH - 1 downto 0);

SIGNAL wrblk : std logic;

SIGNAL wrb : std_logic;

SIGNAL wadr : std logic vector(7 downto 0);

SIGNAL wdata : std logic vector(80 downto 0);

SIGNAL rdblkb_a : std_logic;

SIGNAL rdblkb b : std logic;

SIGNAL rdb_a : std_logic;

SIGNAL rdb b : std logic;

```

```

SIGNAL rdblkb : std_logic;

SIGNAL rdb : std logic;

SIGNAL radr_a : std_logic_vector(7 downto 0);

SIGNAL radr_b : std_logic_vector(7 downto 0);

SIGNAL radr : std logic vector(7 downto 0);

SIGNAL rd_data : std_logic_vector(80 downto 0);

SIGNAL a_idata : std_logic_vector(WIDTH - 1 downto 0);

SIGNAL GND : std logic;

begin

begin

GND <= '0'; -- used to tie off unused inputs to memories

___

-- Register incoming data from the write ports

___

A: if (PIPE = 1) generate

B: process(reset_n, wr_clk)

begin

if (reset_n = '0') then

wrblk_a <= '0';</pre>

wrb a <= '0';

wadr a <= (OTHERS => '0');

wdata a <= (OTHERS => '0');

wrblk b <= '0';</pre>

wrb b <= '0';

wadr b <= (OTHERS => '0');

wdata b <= (OTHERS => '0');

elsif (wr clk'event and wr clk = '1') then

wrblk a <= a wrblkb after 1 ns;</pre>

wrb a <= a wrb after 1 ns;</pre>

wadr a <= a wadr after 1 ns;</pre>

wdata_a <= a_wdata after 1 ns;</pre>

wrblk_b <= b_wrblkb after 1 ns;</pre>

wrb b <= b wrb after 1 ns;</pre>

wadr b <= b wadr after 1 ns;</pre>

wdata_b <= b_wdata after 1 ns;</pre>

end if;

end process;

end generate;

-- Otherwise, just pass them through to the mux

C: if (PIPE /= 1) generate

```

```

wrblk_a <= a_wrblkb;</pre>

wrb a <= a wrb;</pre>

wadr_a <= a_wadr;</pre>

wdata a <= a wdata;

wrblk b <= b wrblkb;

wrb_b <= b_wrb;</pre>

wadr_b <= b_wadr;</pre>

wdata_b <= b_wdata;</pre>

end generate;

-- Multiplex the write ports to the memory

___

wrblk <= wrblk_a when (wr_clk = '1') else wrblk_b;</pre>

wrb <= wrb a when (wr clk = '1') else wrb b;

wadr <= wadr_a when (wr_clk = '1') else wadr_b;</pre>

wdata(80 downto WIDTH) <= (OTHERS => '0'); -- tie off unused bits

wdata(WIDTH - 1 downto 0) <= wdata_a when (wr_clk = '1') else</pre>

wdata b(WIDTH - 1 downto 0);

___

-- IF FOUR-Port and PIPE = 1 Register the read

-- addresses and enables

___

D: if (PMODE = 1 AND PIPE = 1) generate

E: process(reset_n, rd_clk)

begin

if (reset n = '0') then

rdblkb_a <= '0';</pre>

rdb a <= '0';

radr_a <= (OTHERS => '0');

rdblkb b <= '0';</pre>

rdb b <= '0';

radr b <= (OTHERS => '0');

elsif (rd_clk'event and rd_clk = '1') then

rdblkb a <= a rdblkb after 1 ns;

rdb_a <= a_rdb after 1 ns;</pre>

radr a <= a radr after 1 ns;</pre>

rdblkb_b <= b_rdblkb after 1 ns;</pre>

rdb_b <= b_rdb after 1 ns;</pre>

radr b <= b radr after 1 ns;</pre>

end if;

end process;

end generate;

```

```

___

-- Otherwise, it's just a pass them through

___

F: if (PIPE /= 1) generate

rdblkb_a <= a_rdblkb;

rdb_a <= a_rdb;

radr_a <= a_radr;</pre>

rdblkb b <= b rdblkb;

rdb b <= b rdb;

radr b <= b radr;</pre>

end generate;

-- In four-port mode, multiplex the read addresses

-- NOTE: enables are used for output registers only.

W: if (PMODE = 1) generate

radr <= radr a when (rd clk = '1') else radr b;</pre>

end generate;

___

-- IF OREG is 1 (registered), then create the output

-- registers, use rd clk in QPM (PMODE = 1) mode...

___

rd data(80 downto WIDTH) <= (OTHERS => '0'); -- tie off unused bits.

G: if (PMODE = 1 AND OREG = 1) generate

I: process(reset n, rd clk)

begin

if (reset n = '0') then

a_idata <= (OTHERS => '0');

elsif (rd clk'event and rd clk = '0') then

if(rdblkb a = '0' AND rdb a = '0') then

a idata <= rd data(WIDTH-1 downto 0) after 1 ns;

end if;

end if;

end process;

J: process(reset n, rd clk)

begin

if (reset n = '0') then

b_rdata <= (OTHERS => '0');

a rdata <= (OTHERS => '0');

elsif (rd clk'event and rd clk = '1') then

if(rdblkb b = '0' AND rdb b = '0') then

b_rdata <= rd_data(WIDTH-1 downto 0) after 1 ns;</pre>

end if;

if(rdblkb_a = '0' AND rdb_a = '0') then

a rdata <= a idata after 1 ns;

```

end if;

```

end if;

end process;

end generate;

-- In dual port mode - use the write clock for output registers.

___

K: if (PMODE = 0 AND OREG = 1) generate

M: process(reset n, wr clk)

begin

if (reset n = '0') then

a idata <= (OTHERS => '0');

elsif (wr clk'event and wr clk = '0') then

if(a rdblkb = '0' AND a rdb = '0') then

a idata <= rd data(WIDTH-1 downto 0) after 1 ns;

end if;

end if;

end process;

N: process(reset n, wr clk)

begin

if (reset n = '0') then

b rdata <= (OTHERS => '0');

a rdata <= (OTHERS => '0');

elsif (wr clk'event and wr clk = '1') then

if(b_rdblkb = '0' AND b_rdb = '0') then

b_rdata <= rd_data(WIDTH-1 downto 0) after 1 ns;</pre>

end if;

if(a rdblkb = '0' AND a rdb = '0') then

a_rdata <= a_idata after 1 ns;</pre>

end if;

end if;

end process;

end generate;

-- otherwise, assign the output of the

-- memory directly to the read data ports.

___

O: if (OREG /= 1) generate

a_rdata <= rd_data(WIDTH-1 downto 0); -- assign to output ports</pre>

b rdata <= rd data(WIDTH-1 downto 0);</pre>

end generate;

-- IF QPM generate (WIDTH/9) RAM BLOCKS with separate read/write ports

___

Q: if (PMODE = 1) generate

```

```

R: for i in 0 to (WIDTH/9) generate

S: RAM256x9SA

port map( DI8 => wdata((i*9)+8), DI7 => wdata((i*9)+7),

DI6 => wdata((i*9)+6), DI5 => wdata((i*9)+5),

DI4 => wdata((i*9)+4), DI3 => wdata((i*9)+3),

DI2 => wdata((i*9)+2), DI1 => wdata((i*9)+1),

DI0 => wdata((i*9)+0),

WADDR7 => wadr(7), WADDR6 => wadr(6),

WADDR5 => wadr(5), WADDR4 => wadr(4),

WADDR3 => wadr(3), WADDR2 => wadr(2),

WADDR1 => wadr(1), WADDR0 => wadr(0),

WBLKB => wrblk, WRB => wrb,

WCLKS => wr 2xclk,

WPE => open, RPE => open, DOS => open,

RBLKB => GND, RDB => GND,

RADDR7 => radr(7), RADDR6 => radr(6),

RADDR5 => radr(5), RADDR4 => radr(4),

RADDR3 => radr(3), RADDR2 => radr(2),

RADDR1 => radr(1), RADDR0 => radr(0),

DO8 => rd data((i*9)+8), DO7 => rd data((i*9)+7),

DO6 => rd data((i*9)+6), DO5 => rd data((i*9)+5),

DO4 => rd data((i*9)+4), DO3 => rd data((i*9)+3),

DO2 => rd data((i*9)+2), DO1 => rd data((i*9)+1),

DO0 => rd data((i*9)+0),

PARODD => GND, DIS => GND

);

end generate;

end generate;

-- IF DPM generate (WIDTH/9) RAM BLOCKS with combined read/write ports

-- ie: use muxed write address for the read address also.

___

T: if (PMODE = 0) generate

U: for i in 0 to (WIDTH/9) generate

V: RAM256x9SA

port map( DI8 => wdata((i*9)+8), DI7 => wdata((i*9)+7),

DI6 => wdata((i*9)+6), DI5 => wdata((i*9)+5),

DI4 => wdata((i*9)+4), DI3 => wdata((i*9)+3),

DI2 => wdata((i*9)+2), DI1 => wdata((i*9)+1),

DIO => wdata((i*9)+0),

WADDR7 => wadr(7), WADDR6 => wadr(6),

WADDR5 => wadr(5), WADDR4 => wadr(4),

WADDR3 => wadr(3), WADDR2 => wadr(2),

WADDR1 => wadr(1), WADDR0 => wadr(0),

```

```

WBLKB => wrblk, WRB => wrb,

WCLKS => wr_2xclk,

WPE => open, RPE => open, DOS => open,

RBLKB => GND, RDB => GND,

RADDR7 => wadr(7), RADDR6 => wadr(6),

RADDR5 => wadr(5), RADDR4 => wadr(4),

RADDR3 => wadr(3), RADDR2 => wadr(2),

RADDR1 => wadr(1), RADDR0 => wadr(0),

DO8 => rd_data((i*9)+8), DO7 => rd_data((i*9)+7),

DO6 => rd_data((i*9)+6), DO5 => rd_data((i*9)+5),

DO4 => rd_data((i*9)+4), DO3 => rd_data((i*9)+3),

DO2 => rd data((i*9)+2), DO1 => rd data((i*9)+1),

DO0 => rd_data((i*9)+0),

PARODD => GND, DIS => GND

);

end generate;

end generate;

end RTL;

```

18

# List of Changes

The following table shows important changes made in this document for each revision.

| Revision                  | Changes                | Page |

|---------------------------|------------------------|------|

| Revision 1<br>(June 2016) | Non-technical updates. | N/A  |

| Revision 0<br>(July 2003) | Initial release.       | N/A  |

Power Matters."

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 E-mail: sales.support@microsemi.com www.microsemi.com

© 2016 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 4,800 employees globally. Learn more at www.microsemi.com.