## MicroNote 135

## **1** Failure Mechanisms for Transient Voltage Suppressors

#### **By Kent Walters**

In most applications, anticipated transient threats—like open-circuit-transient voltage (Voc) and shortcircuit current (lsc)—are well defined in the RTCA DO-160 specification for avionics and in international standards such as IEC-1000-4-2, IEC-1000-4-4, and IEC-1000-4-5. From these values, the peak pulse current (IPP) and peak pulse power (PPP) can be determined, as described in MicroNotes 125, 126, and 127, for properly selecting a TVS to ensure adequate surge capabilities. However, in some applications, the information for quantifying transients and their sources is not well defined due to the obscure overall nature of various possible transient events.

This can eventually lead to questions about what failure mechanisms exist for silicon p-n junction transient voltage suppressor (TVS) when overstressed. This becomes important, because it is located in front of a sensitive load as a parallel shunt path to redirect any high voltage transient threats to ground before they damage the load it is intended to protect.

**Note**: When a TVS is properly selected in voltage, it is transparent to the circuit, or simply idling at a very low standby current ( $I_D$ ) less than or equal to its rated reverse standoff voltage ( $V_{WM}$ ), until a higher transient voltage occurs that drives the device briefly into its avalanche breakdown region.

The silicon p-n junction TVS device is also identified as an "ABD," or avalanche breakdown diode transient voltage suppressor in IEC or JEDEC standards, such as JESD210. When avalanche breakdown occurs, the silicon p-n junction device conducts a large amount of current (IPP) to ground in front of the protected load for a short duration transient that is typically 1 ms or less. During this short event, the TVS device clamps the voltage to a safe level (Vc). This also results in significant power (PPP) and heating at the p-n junction. This can repeat itself for random recurring transient events indefinitely within the rating of the TVS, but only if there is sufficient time for the device to cool before the next event occurs. Rapid repetitive surges that would cause cumulative heating effects are not part of the normal rating of a TVS, as described in MicroNote 133. Silicon p-n junction TVS devices are unlike metal oxide varistor (MOV) devices that can degrade over time after many random recurring surges within their maximum rating.

When individual excessive surges occur beyond the rating of the TVS, these devices can fail just like any other semiconductor component when exceeding their ratings. For TVSs, this primarily involves excessive peak pulse power (P<sub>PP</sub>) and/or peak pulse current (I<sub>PP</sub>). The basic form of failure mechanism is attributable to excessive heat in the active p-n junction of the silicon element. This is also dependent on the pulse width of the transient threat where P<sub>PP</sub> capabilities for a TVS decline in a predictable manner with longer pulse widths (as described in MicroNotes 104 and 120). The capabilities in P<sub>PP</sub> generally follow what has historically been recognized as a Wunsch-Bell Curve.

## 2 Exceeding TVS Peak Pulse Power Ratings

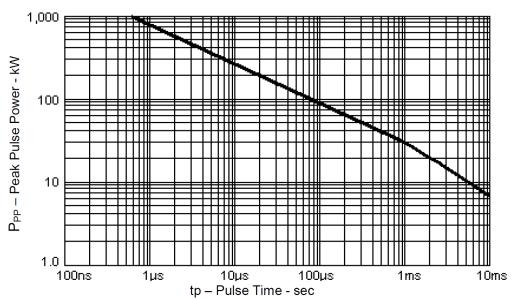

The P<sub>PP</sub> versus pulse time performance curve—found in Figure 1 (see page 2) of most of the Microsemi datasheets—is a straight line with a negative slope on a log-log plot. It is typically shown for short transients up to 1 ms (sometimes longer) for most device types. The negative slope in these figures declines one decade in P<sub>PP</sub> for every two decades in increasing pulse width. In mathematical terms, the P<sub>PP</sub> is inversely proportional to the square root of pulse width.

This relationship for rating a TVS and its maximum P<sub>PP</sub> capabilities correlate to a relatively constant elevated p-n junction temperature before failure, regardless of pulse duration time. These p-n junction temperatures can briefly approach 275 °C during the surge without damaging the device. The example shown below is for a 30 kW rated TVS device at 1 ms and 25 °C. For higher device or ambient temperatures, the P<sub>PP</sub> capabilities are derated as also shown in most TVS datasheets and described in MicroNotes 114 and 115.

Figure 1 • Figure 1: Peak Pulse Power vs Pulse Time

This same characteristic behavior is also shown for other Microsemi TVS product datasheets where devices with lower P<sub>PP</sub> ratings will portray the same negative slope, except they are positioned lower with respect to the ordinate (P<sub>PP</sub>) axis. The intersection at 1 ms will coincide with its P<sub>PP</sub> rating at 25 °C if referenced at 10/1000  $\mu$ s. This is the industry method of identifying a double exponential impulse with a 10  $\mu$ s rise time to the peak and a 1000  $\mu$ s to the 50% decay point.

## 3 TVS Failure Mechanisms

With that background, we can better describe specific failure mechanisms when TVSs are pushed above their  $P_{PP}$  ratings, and where p-n junction temperatures start exceeding a safe operating level during a surge event. The extent that a surge exceeds specified  $P_{PP}$  ratings may also dictate failure mode and its severity.

## 4 Hot Spots and Electrical Shorts

In the vast majority of cases, a TVS will fail in a shorted or severely degraded mode when overstressed. This has often been the preferred failure mode for many applications, since the device would then protect the remaining sensitive circuit from further severe transient threats due to its "electrically shorted" shunt path to ground in front of the protected load until the device is replaced.

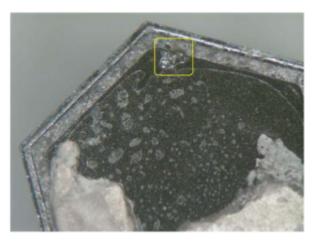

As p-n junction temperatures quickly increase during a transient beyond device ratings, it eventually forces the device into its "intrinsic" region where it no longer operates as a semiconductor and instead becomes a resistor. This occurs when the concentration of thermally generated electron-hole pairs at high temperatures approaches or exceeds the background p or n doping levels of a TVS device, thus compromising the semiconductor characteristic features of the p-n junction. This will initially occur in higher voltage TVS devices that have a lower concentration in background doping level for higher avalanche breakdown voltages as dictated by the overall semiconductor physics in diode device designs. When that happens at very high p-n junction temperatures, the TVS device voltage characteristics start to collapse due to excessive leakage currents during the transient event. Thermal runaway will quickly occur. This collapse in voltage features of the TVS may also include the possibility of high "follow-on currents" through the device, depending on the operating voltage and load-line features of the circuit it is in. This rapid failure mode typically creates a "hot spot" somewhere in the p-n junction, as well as permanent damage up to and including a localized silicon melt region from front to back of the active die element. That feature becomes very destructive as is evident in a physical analysis shown below.

#### Figure 2 • Figure 2: Hot Spot Failure Mode

This described localized-melt region is an alloy formation of silicon, combined with adjoining ohmiccontact metallization or solder materials, resulting in a highly conductive "pipe" region from front to back of the silicon die. It may also result in micro cracks from thermal stresses propagating outward from the hot-spot region. Although these secondary cracks in the active silicon die will also increase leakage current and voltage degradation, the major failure mechanism is the hot spot itself.

This very rapid catastrophic event during a transient electrical over stress (EOS) also explains why there are very few (if any) occurrences of only slight degradation due to a surge overstress. It has either failed in a significant manner due to thermal runaway, or it is still good. The described mode of degradation (if not shorted) is where the TVS silicon internal element only supports a minimal value in voltage with very high leakage currents and minimal resistance—a few ohms or less.

In other application scenarios where an excessive amount of dc voltage or current (power) is applied, the device will be driven into continuous breakdown similar to a zener. If that dc power is excessive, it will also eventually overheat if it is not fused open by design on the line being protected by the TVS. During this period of time, the breakdown voltage will again rise due to the positive temperature coefficient of avalanche breakdown for V<sub>Z</sub> or V<sub>BR</sub>, as would a zener (see Micronote 203). Several scenarios of operating a TVS as a zener, or vice-versa, are discussed in MicroNote 134. The amount of heating (and voltage rise) with continuous applied power is also dependent on heat sinking provided to the device. The maximum voltage may briefly approach the maximum clamping voltage (Vc) from similar high p-n junction temperatures as earlier noted during surge. This is primarily due to the positive temperature coefficient of avalanche breakdown. Before device failure, it still can serve as a shunt regulator protecting a load from excessive voltages. However this type of sustained heating is not desirable and can eventually reflow internal solders (if applicable) closest to the p-n junction where notable energy (heat) is generated with applied power and time. If localized hot spots are again generated by solder reflow either around or through the p-n junction.

## 5 Loss of Contact and Electrical Opens

In most applications, loss of contact, or electrical opens, is not a desirable EOS failure mode for a TVS in its shunt protective position in the circuit, because that would expose the remaining sensitive load to subsequent transient threats. An electrical open of the TVS location can also make it difficult to verify whether anything is wrong until a subsequent surge occurs that may damage the remaining circuit requiring protection. Nevertheless, for some severe forms of EOS, this failure mode can occur with TVS devices. In those unusual circumstances, the following information is provided to further describe possible failure modes and how to minimize their occurrence.

## 6 Avoiding Electrical Opens

To avoid electrical open failure in the TVS location of the circuit, precautions must be taken in how package termination(s) are attached or heat sunk. This prevents the risk of them being either broken or melted off from a sustained heat soak, which can often follow a surge event or sustained power overload. A further extended heat soak can occur if a TVS failure does not become a dead short and must still dissipate significant sustained power with very high follow-on currents. This is particularly a concern if there is minimal source resistance in the circuit (such as a power buss). For these reasons, a fuse can also be placed in the circuit to prevent overheating of PCB traces or a severely degraded TVS component that may still be dissipating power in a low resistive state without completely shorting electrically.

TVS designs using a double-plug glass body configuration can break mechanically in half when severely overstressed, resulting in an electrical open. The probability of this type of failure mechanism increases as the severity of transient power increases beyond the device ratings. When the die is quickly heated to extremes by a severe transient and expands rapidly between two plugs surrounded by a glass body, there is no internal strain relief mechanism. In those cases, it ultimately breaks the glass body into two parts at the location of the active die element. Conservative selection in P<sub>PP</sub> for TVSs beyond the expected threat level requirements will minimize these catastrophic failure modes. This includes consideration for P<sub>PP</sub> temperature derating, described in MicroNotes 114 and 115.

In small size TVS array designs involving internal wire bonds that are only intended for very short transients of  $8/20 \ \mu$ s or less, such as in ESD protection, there are other possible failure modes when exceeding Ppp ratings for these smaller devices. The internal wire bond designs used in these smaller designs between the die and package lead frame can fuse open. Small individual internal wire bonds are not used on higher Ppp rated TVSs where large lead or lead-frame contacts are bonded directly to the active TVS element. For hybrid applications requiring the use of larger TVS die or chips, it is recommended to use multiple wire bonds. Also, a metal disc bonded to the top side of the die should be used before wire bonding to the disc. This serves as a "current-spreader" across the face of the die, rather than allow high surge current concentrations to occur under a wire bond. The disc can also serve as a heat sink for a short transient to make for a more efficient application of the active die size used.

Despite design precautions from various known transient threats, some transients can also be allusive by their very nature. For example, there can be extreme transients with sufficient energy—like close proximity lightning strikes or nearby severe inductive load switching—that can cause the TVS device to vaporize at its weakest points from extreme P<sub>PP</sub> energy levels causing an electrical open. However, these types of events are rare compared to the other failure mechanisms described in this MicroNote.

# 7 Conservative TVS Design Options

Redundant circuits are often used in very conservative design applications where any failure becomes critical—like in satellites, for example. Using that same principle, TVSs may be applied in such a manner where any single component failure will not significantly affect the application. For example, two TVS devices may be placed in series where twice the clamping voltage (Vc) of any one TVS device is still adequate to protect the sensitive load behind the TVS and the working standoff voltage (VwM) of one device. If any one TVS device in series becomes electrically shorted or severely degraded, the remaining device in series still provides protection. As described earlier, a TVS device is simply idling at very low leakage current in its normal operating mode at VwM until a high voltage transient drives it into avalanche breakdown. Higher voltage selections of VwM will not be an issue unless the Vc is excessive for the needed sensitive load protection. This includes the effects resulting from two TVS devices in series. However, in many applications, the sensitive load being protected does not allow much voltage overhead. More on that subject is discussed in MicroNote 134.

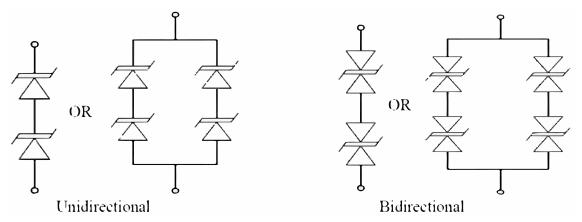

In those cases where an unusual electrical open of any one TVS device may be of concern, two such legs of TVSs are provided in parallel, representing a total of four TVS devices. Such configurations for TVSs also increase the P<sub>PP</sub> capabilities for conservative design as described in MicroNotes 112 and 113. These conservative application methods can also be used with unidirectional or bidirectional TVS devices as shown.

#### Figure 3 • Figure 3: Conservative TVS Circuit Designs

#### 7.1 Summary

In summary, the primary failure mode of TVSs is a severely degraded device that has collapsed in voltage or become an electrical short. Nevertheless, there can be other failure modes depending on the severity of electrical overstress. Using conservative approaches by selecting TVSs with generous P<sub>PP</sub> ratings helps diminish other less desirable failure modes.

# 8 Contact

For additional technical information, please contact Design Support at: http://www.microsemi.com/designsupport or Kent Walters (kwalters@microsemi.com) at 480-302-1144

## 9 References

[1] Clark, O.M. and Walters, K. MicroNote<sup>™</sup> No. 104, Microsemi Corp., 1994 [2] Clark, O.M. and Walters, K. MicroNote<sup>™</sup> No. 112, Microsemi Corp., 1994 [3] Clark, O.M. and Walters, K. MicroNote<sup>™</sup> No. 113, Microsemi Corp., 1994 [4] Clark, O.M. and Walters, K. MicroNote<sup>™</sup> No. 114, Microsemi Corp., 1994 [5] Clark, O.M. and Walters, K. MicroNote<sup>™</sup> No. 115, Microsemi Corp., 1994 [6] Walters, K. MicroNote<sup>™</sup> No. 120, Microsemi Corp., 1996 [7] Walters, K. MicroNote<sup>™</sup> No. 125, Microsemi Corp., 1999 [8] Clark, O.M. MicroNote<sup>™</sup> No. 126, Microsemi Corp., 2004 [9] Clark, O.M. MicroNote<sup>™</sup> No. 127, Microsemi Corp., 2005 [10] Walters, K. MicroNote<sup>™</sup> No. 133, Microsemi Corp., 2010 [11] Walters, K. MicroNote<sup>™</sup> No. 134, Microsemi Corp., 2010 [12] Walters, K. and Clark, O.M. MicroNote<sup>™</sup> No. 203, Microsemi Corp., 1995 [13] RTCA/DO-160G, Section 22 [14] JESD210 [15] IEC-1000-4-2 [16] IEC-1000-4-4

[17] IEC-1000-4-5

Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

© 2018 Microsemi. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mision-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is provident y to Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAS, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions; security technologies and scalable anti-tamper products; thermet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www microsemi.com.