# UG0931 User Guide RT PolarFire FPGA User I/O

a MICROCHIP company

#### Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

Email: sales.support@microsemi.com www.microsemi.com

©2021 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### About Microsemi

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# **Contents**

| 1 | Revisi | on Hist          | ory                                                            | 1   |

|---|--------|------------------|----------------------------------------------------------------|-----|

|   | 1.1    | Revision         | 11.0                                                           | . 1 |

| 2 | I/O 0\ | erview/          |                                                                | 2   |

|   | 2.1    | GPIO ar          | nd HSIO Features                                               | . 2 |

|   |        | 2.1.1            | GPIO Features                                                  |     |

|   |        | 2.1.2            | HSIO Features                                                  | . 2 |

|   | 2.2    | Supporte         | ed I/O Standards                                               | . 3 |

|   |        | 2.2.1            | I/O Standard Descriptions                                      | . 5 |

|   | 2.3    | I/O Bank         | (S                                                             | . 9 |

|   | 2.4    | Supply \         | /oltages for RT PolarFire FPGA I/O Banks                       | 10  |

|   | 2.5    | RT Pola          | rFire FPGA I/O Overview                                        |     |

|   |        | 2.5.1            | Single-Ended Transmitter and Receiver Mode                     |     |

|   |        | 2.5.2            | Differential Transmitter Mode                                  |     |

|   |        | 2.5.3<br>2.5.4   | Differential Receiver Mode  I/O Digital (IOD)                  |     |

|   | 2.6    | -                | itive                                                          |     |

|   | 2.0    | I/O FIIII        | iuve                                                           | 12  |

| 3 | I/O Fe | atures           | and Implementation                                             | 13  |

|   | 3.1    | I/O Anal         | og (IOA) Buffer Programmable Features                          |     |

|   |        | 3.1.1            | Slew Rate Control                                              |     |

|   |        | 3.1.2            | Programmable Weak Pull- Up/Down and Bus-Keeper (Hold) Circuits |     |

|   |        | 3.1.3<br>3.1.4   | Schmitt Trigger Input Hysteresis                               |     |

|   |        | 3.1.5            | Programmable Output Impedance Control                          |     |

|   |        | 3.1.6            | Differential Near End Termination                              |     |

|   |        | 3.1.7            | On-Die Termination (ODT)                                       | 17  |

|   |        | 3.1.8            | Common Mode Voltage (Vcm) Settings                             |     |

|   |        | 3.1.9            | Programmable Clamp Diode                                       |     |

|   |        | 3.1.10<br>3.1.11 | Compensated Drive Impedance and Terminations                   |     |

|   |        | 3.1.12           | Shield                                                         |     |

|   |        | 3.1.13           | Open Drain GPIO                                                |     |

|   | 3.2    | I/O Imple        | ementation Considerations                                      | 21  |

|   |        | 3.2.1            | Reference Voltage for I/O Bank                                 | 22  |

|   |        | 3.2.2            | Mixed IO in VDDI Banks                                         |     |

|   |        | 3.2.3<br>3.2.4   | I/O External Termination                                       |     |

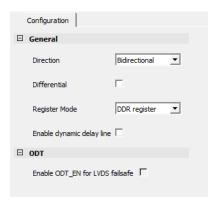

|   |        | 3.2.4            | Implementing MIPI D-PHY                                        |     |

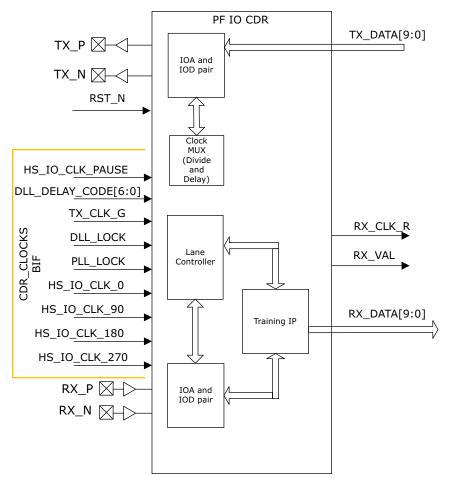

|   |        | 3.2.6            | I/O States During Various Operational Modes                    |     |

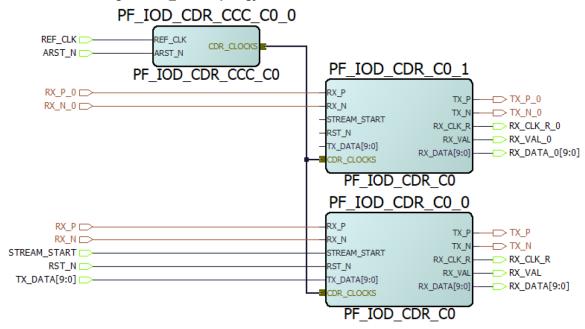

|   |        | 3.2.7            | Cold Sparing and Hot Swap                                      |     |

|   |        | 3.2.8            | IO Glitches                                                    |     |

|   |        | 3.2.9            | IO Calibration                                                 |     |

|   |        | 3.2.10<br>3.2.11 | Dynamic ODT or Fail-Safe LVDS                                  |     |

|   |        | 3.2.11           | Transceiver Receivers, Transmitters and Reference Clock Inputs |     |

| 4 | 105.5  |                  |                                                                |     |

| 4 |        |                  | s and User Modes                                               |     |

|   | 4.1    |                  | ck Features                                                    |     |

|   | 4.2    |                  | ck Overview                                                    |     |

|   |        | 4.2.1            | Programmable I/O Delay                                         | აღ  |

| Microsem            | 1 |

|---------------------|---|

| a MICROCHIP COMPANY |   |

|   |            | 4.2.2          | I/O Registers                                                               |     |

|---|------------|----------------|-----------------------------------------------------------------------------|-----|

|   |            | 4.2.3          | I/O Gearing                                                                 |     |

|   |            | 4.2.4          | I/O FIFO                                                                    |     |

|   | 4.3        |                | rFire FPGA I/O Lanes                                                        |     |

|   |            | 4.3.1          | Lane Controller                                                             |     |

|   |            | 4.3.2          | I/O Lanes in Each Bank                                                      |     |

|   | 4.4        |                | k Networks                                                                  |     |

|   |            | 4.4.1<br>4.4.2 | Global Clock Resource Regional Clock Networks                               |     |

|   |            | 4.4.2          | Lane Clock Resources                                                        |     |

|   |            | 4.4.4          | High-Speed I/O Bank Clock Resource (HS_IO_CLK)                              | 46  |

|   |            | 4.4.5          | Bit Slip                                                                    |     |

|   | 4.5        | RT Pola        | rFire FPGA Generic I/O Interfaces                                           |     |

|   |            | 4.5.1          | RX DDR Interfaces                                                           |     |

|   |            | 4.5.2          | RX_DDR_G_A/ RX_DDR_R_A—Aligned Interfaces with Static Delays                | 49  |

|   |            | 4.5.3          | RX_DDR_G_C and RX_DDR_R_C—Centered Interfaces with Static Delays            |     |

|   |            | 4.5.4          | RX_DDRX_B_G_C and RX_DDRX_B_G_A/RX_DDRX_B_R_A Interfaces with Static Delays | S.  |

|   |            | 455            | 54  BY DDD Freetienel Alienad/Freetienel Dunarie Interferee                 | EE  |

|   |            | 4.5.5<br>4.5.6 | RX_DDR Fractional Aligned/Fractional Dynamic Interfaces                     |     |

|   |            | 4.5.7          | TX DDR Interfaces                                                           |     |

|   | 4.6        | -              | TX DDX Interiores                                                           |     |

|   | 4.0        | Latericy       |                                                                             | 00  |

| 5 | Gener      | ic IOD         | Interface Implementation                                                    | 61  |

|   | 5.1        |                | e Primitives                                                                |     |

|   |            | 5.1.1          | Input DELAY                                                                 |     |

|   |            | 5.1.2          | Input Register (IREG)                                                       |     |

|   |            | 5.1.3<br>5.1.4 | Input FIFO                                                                  |     |

|   | <b>5</b> 0 | -              | Input Gear Box                                                              |     |

|   | 5.2        | 5.2.1          | ace Configurators                                                           |     |

|   |            | 5.2.1          | IOD Generic RX                                                              |     |

|   |            | 5.2.3          | Dynamic Delay Control                                                       |     |

|   |            | 5.2.4          | IOD Generic TX                                                              |     |

|   | 5.3        | Basic I/0      | O Configurator                                                              |     |

| _ |            |                |                                                                             |     |

| 6 | Protoc     |                | cific I/O Interfaces                                                        |     |

|   | 6.1        |                | _CDR                                                                        |     |

|   |            |                | IOD CDR                                                                     |     |

|   |            | 6.1.2          |                                                                             |     |

|   |            | 6.1.3<br>6.1.4 | Transmit Interface                                                          |     |

|   |            | 6.1.5          | Clock Sharing                                                               |     |

|   | 6.2        |                | o GMII Converter                                                            |     |

|   | 6.3        |                | 1                                                                           |     |

|   | 0.5        | 6.3.1          | 7:1 LVDS Receive Interface                                                  |     |

|   |            | 6.3.2          | 7:1 LVDS Transmit Interface                                                 |     |

| _ | _          |                |                                                                             |     |

| 7 | •          |                | Interface Training                                                          |     |

|   | 7.1        |                | Data Margin Training                                                        |     |

|   | 7.0        | 7.1.1          | HS_IO_CLK and System Clock Training                                         |     |

|   | 7.2        |                | ODBitAlign                                                                  |     |

|   |            | 7.2.1<br>7.2.2 | CoreRxIODBitAlign Training Algorithm                                        |     |

|   |            | 7.2.2          | CoreRxIODBitAlign Ports                                                     |     |

|   |            | 1 .2.0         |                                                                             | U Z |

# **Figures**

| Figure 1               | RTPF500T Device I/O Banks                                       |    |

|------------------------|-----------------------------------------------------------------|----|

| Figure 2               | RT PolarFire FPGA I/O Pair                                      |    |

| Figure 3               | RT PolarFire FPGA I/O Pair (Detailed View)                      | 13 |

| Figure 4               | SSTL25 and SSTL18 Stub Resistor                                 | 21 |

| Figure 5               | Open Drain GPIO Example                                         | 21 |

| Figure 6               | SLVSE System Diagram                                            | 25 |

| Figure 7               | Bus-LVDSE System Diagram                                        |    |

| Figure 8               | MLVDSE System Diagram                                           |    |

| Figure 9               | LVPECL System Diagram                                           |    |

| Figure 10              | MIPI D-PHY Receiver                                             |    |

| Figure 11              | MIPI D-PHY Transmit Interface                                   |    |

| Figure 12              | MIPI D-PHY Transmit Interface (High-speed and Low-power)        |    |

| Figure 13              | High-Speed Transmit with Bidirectional                          |    |

| Figure 14              | Dynamic ODT used for Failsafe LVDS                              |    |

| Figure 15              | IOD Configured for I/O Registers                                |    |

| Figure 16              | IOD Input Delay Example                                         |    |

| Figure 17              | I/O Registers in IOD                                            |    |

| Figure 18              | Input Register                                                  |    |

| Figure 19              | Output Register                                                 |    |

| Figure 20              | Enable Register                                                 |    |

| Figure 21              | I/O Register Combining from Place and Route Layout Options      |    |

| Figure 22              | I/O Digital                                                     |    |

| Figure 23              | RT PolarFire FPGA I/O Lanes                                     |    |

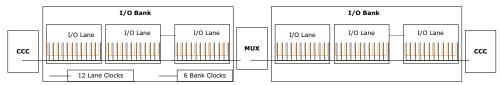

| Figure 24              | Distribution of the Lane Clock                                  |    |

| Figure 25              | Distribution of the HS_IO_CLK                                   |    |

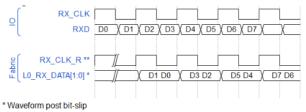

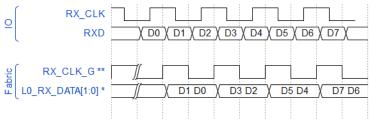

| Figure 26              | Aligned Data and Clock Waveform                                 |    |

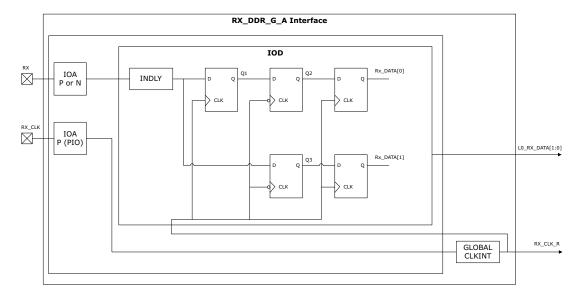

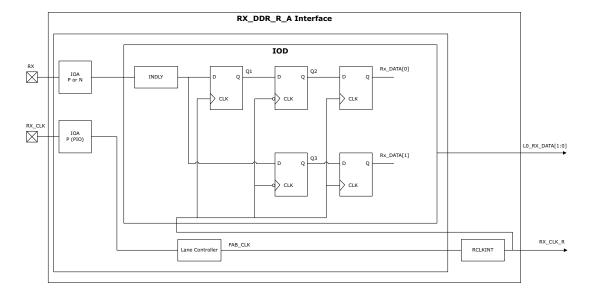

| Figure 27              | RX DDRX1 Aligned Interface Using Global Clock                   |    |

| Figure 28              | RX_DDRX1 Aligned Interface Using Regional Clock                 |    |

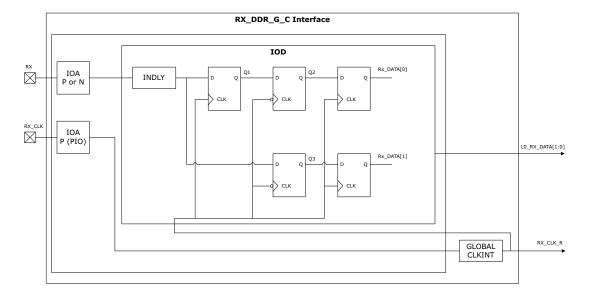

| Figure 29              | Centered Data and Clock Waveform                                |    |

| Figure 30              | RX_DDRX1 Centered Interface Using Global Clock                  |    |

| Figure 31              | RX_DDRX1 Centered Interface Using Regional Clock                |    |

| Figure 32              | Rx geared Waveform                                              |    |

| Figure 33              | Fractional Aligned Data and Clock Waveform                      |    |

| Figure 34              | RX_DDRX_B_G_DYN/ RX_DDRX_B_R_DYN Waveform                       |    |

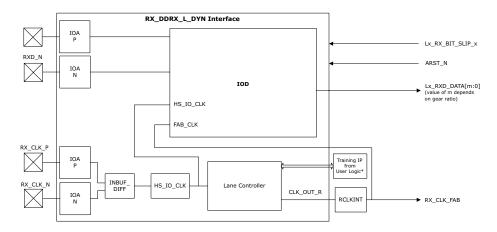

| Figure 35              | Block Diagram of the RX_DDRX_B_G_DYN/ RX_DDRX_B_R_DYN Interface |    |

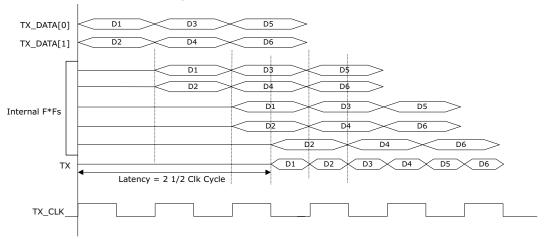

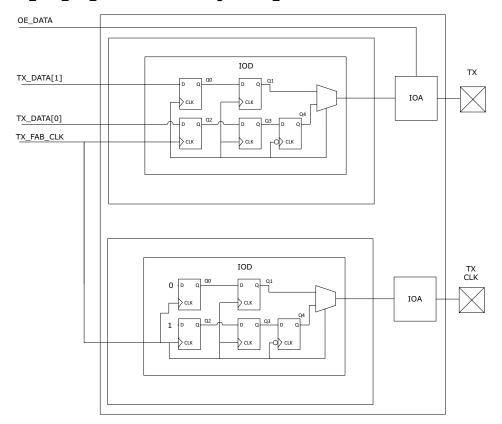

| Figure 36              | TX DDR G A Interface Signal Waveform—TXDDRX1                    |    |

| •                      | TX_DDR_G/B_A Interface Block Diagram—TX_DDRX1                   | 50 |

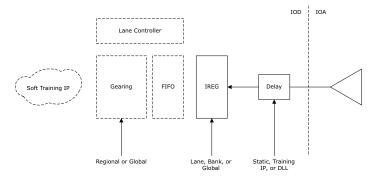

| Figure 37              | IOD Modules used within a Generic DDRX I/O Interface            | 62 |

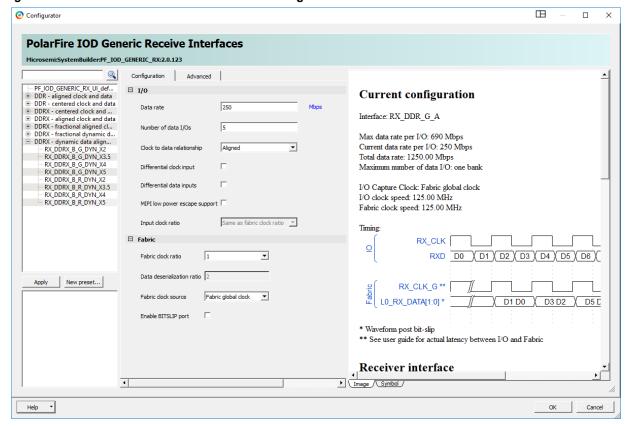

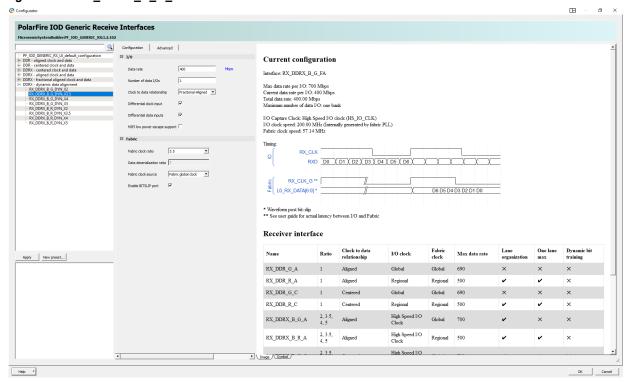

| Figure 38<br>Figure 39 | IOD Generic Receive Interfaces—Configuration Tab                |    |

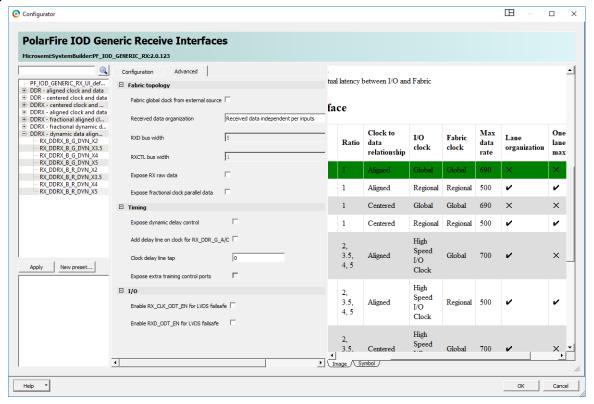

| Figure 39              | IOD Generic Receive Interfaces—Configuration Tab                |    |

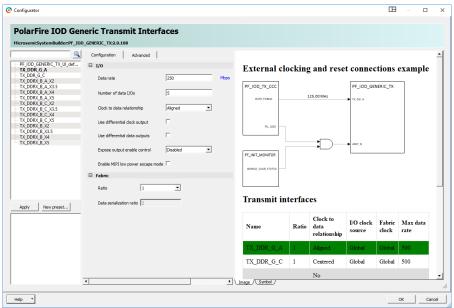

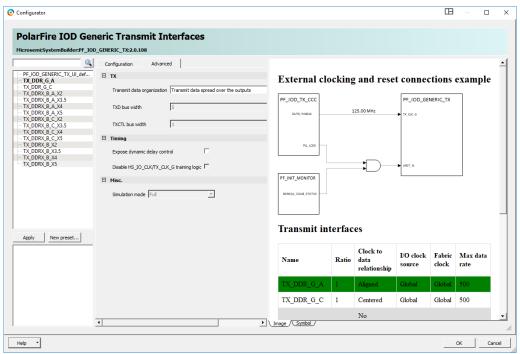

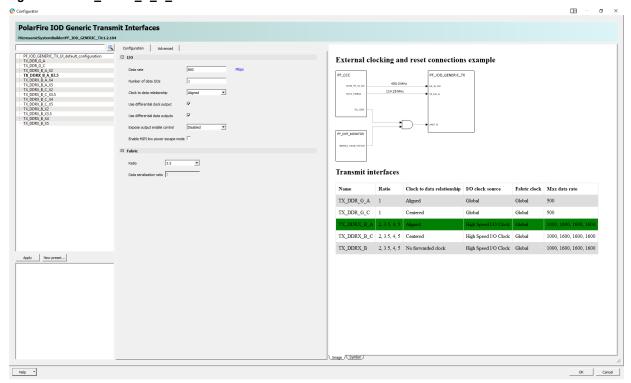

| Figure 40              | IOD Generic Transmit Interfaces—Advanced Tab                    |    |

|                        | IOD Generic Transmit Interfaces—Configuration Tab               |    |

| Figure 42              |                                                                 |    |

| Figure 43              | RT PolarFire IO Configurator                                    |    |

| Figure 44              | IO Configuration Tab                                            |    |

| Figure 45              | PF_IOD_CDR Transmit and Receive Interface Modes                 |    |

| Figure 46              | SmartDesign of IOD_CDR Topology                                 |    |

| Figure 47              | IOD CDR Configuration                                           |    |

| Figure 48              | Using PF_IOD_CDR Interfaces                                     |    |

| Figure 49              | Multiple PF_IOD_CDR Transmit and Receive Interfaces             |    |

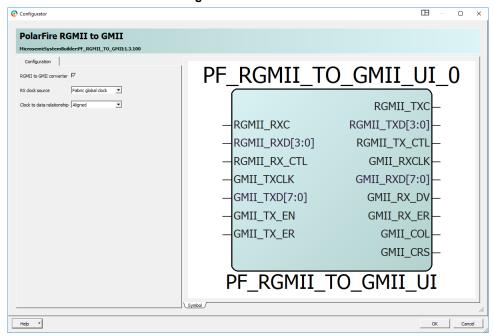

| Figure 50              | RGMII to GMII Block Diagram                                     |    |

| Figure 51              | RT PolarFire RGMII to GMII Configurator                         |    |

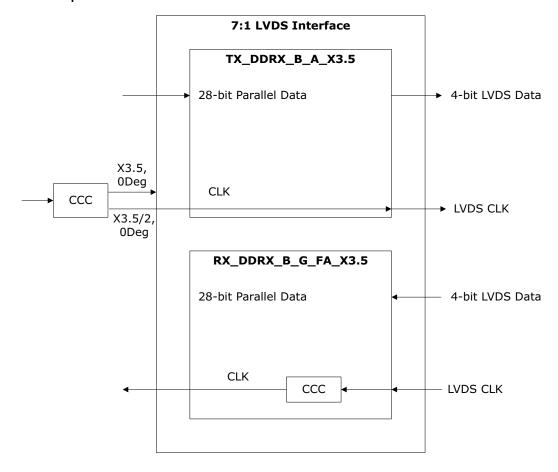

| Figure 52              | Example of 7:1 LVDS Interface—Four Data and One Clock           |    |

| Figure 53              | RX_DDRX_B_G_FA Interface                                        |    |

| Figure 54              | TX DDRX B A X3.5                                                | 83 |

| Figure 55 | Clock to Data Training Data Path         | 84 |

|-----------|------------------------------------------|----|

| Figure 56 | IOD Training Block Diagram               | 85 |

| Figure 57 | HS_IO_CLK to SYSCLK Data Transfer        | 86 |

| Figure 58 | SYSCLK to HS_IO_CLK Data Transfer        | 87 |

| Figure 59 | SYSCLK to HS_IO_CLK Before Training      | 87 |

| Figure 60 | SYSCLK to HS_IO_CLK After Training       | 87 |

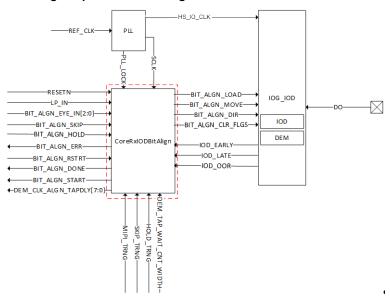

| Figure 61 | CoreRxIODBitAlign Implementation Diagram | 88 |

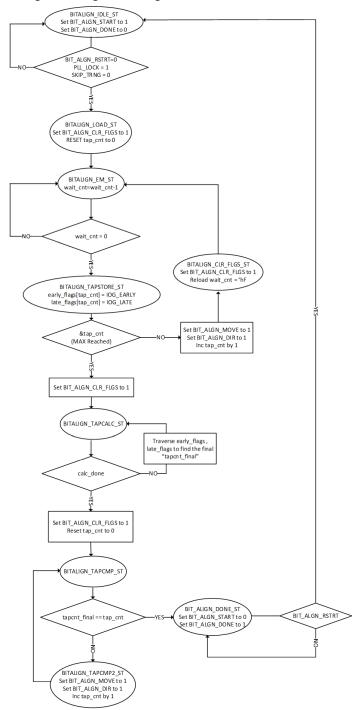

| Figure 62 | CoreRxIODBitAlign Training State Diagram | 89 |

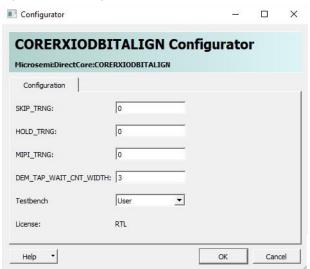

| Figure 63 | CoreRxIODBitAlign Libero Configurator    |    |

# **Tables**

| Table 1  | Supported I/O                                              | . 3 |

|----------|------------------------------------------------------------|-----|

| Table 2  | Supply Pin                                                 | 10  |

| Table 3  | Slew Rate Control                                          | 14  |

| Table 4  | Weak Pull and Bus-Keeper Control                           | 15  |

| Table 5  | Schmitt Trigger Control                                    |     |

| Table 6  | Programmable Drive Strength Control                        |     |

| Table 7  | Programmable Output Impedance Standards                    |     |

| Table 8  | Source Termination Support                                 |     |

| Table 9  | ODT Support in GPIO and HSIO                               |     |

| Table 10 | Programmable Differential Termination Control              |     |

| Table 11 | Programmable Clamp Diode                                   |     |

| Table 12 | GPIO LVTTL/LVCMOS I/O Compatibility in Receive Mode        |     |

| Table 13 | HSIO LVCMOS I/O Compatibility in Receive Mode              |     |

| Table 14 | GPIO Mixed Reference Receiver Mode                         |     |

| Table 15 | HSIO HSUL12/HSTL12/POD I/O Compatibility in Receive Mode   |     |

| Table 16 | GPIO Differential I/O Compatibility in Receive Mode        |     |

| Table 17 | I/O External Termination with ODT Off                      |     |

| Table 17 |                                                            |     |

| _        | I/O States during Power-Up and Initialization              |     |

| Table 19 | GPIO and HSIO States During Programming Modes              |     |

| Table 20 | Dedicated IOs—Fixed Settings                               |     |

| Table 21 | I/O Input Register Ports                                   |     |

| Table 22 | I/O Output Register Ports                                  |     |

| Table 23 | I/O Register Ports                                         |     |

| Table 24 | I/O Lanes in Each Bank                                     |     |

| Table 25 | RT PolarFire Device Support for Generic RX DDR interfaces, | 49  |

| Table 26 | RX_DDR Aligned Interface Mode Ports                        |     |

| Table 27 | RX_DDR Centered Interface Mode Ports                       |     |

| Table 28 | RX_DDR_B_C and RX_DDR_B_A Interface Mode Ports             |     |

| Table 29 | Fractional Aligned Interface Mode Ports                    | 56  |

| Table 30 | RX_DDRX_L_DYN Ports                                        | 58  |

| Table 31 | TX DDR Interfaces                                          | 58  |

| Table 32 | TX_DDR_G/B_A Interface Mode Ports                          | 60  |

| Table 33 | Latency for the Rx/Tx CLK Interface                        |     |

| Table 34 | Receive Interface                                          | 63  |

| Table 35 | IOD Generic Receive Interfaces—Configuration Tab           | 64  |

| Table 36 | IOD Generic Receive Interfaces—Advanced Tab                | 65  |

| Table 37 | Dynamic Delay Control Ports                                |     |

| Table 38 | Transmit Interface                                         |     |

| Table 39 | IOD Generic Transmit Interfaces—Configuration Tab          |     |

| Table 40 | IOD Generic Transmit Interfaces—Advanced Tab               |     |

| Table 41 | PF_IOD_CDR Interface Associated Ports                      |     |

| Table 42 | IOD CDR Configuration                                      |     |

| Table 43 | Advanced Tab Options                                       |     |

| Table 44 | Advanced Diagnostic Ports                                  |     |

| Table 45 | 1GbE and SGMII IOCDR Per Device/Package                    |     |

| Table 46 | GMII Ports                                                 |     |

| Table 47 | CoreRxIODBitAlign Interface Parameters                     |     |

| Table 48 |                                                            | 92  |

|          |                                                            |     |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the current publication.

# **1.1** Revision **1.0**

The first publication of this document.

# 2 I/O Overview

RT PolarFire<sup>®</sup> device user I/Os support multiple I/O standards while simultaneously providing the high bandwidth needed to maximize the internal logic capabilities of the device and achieve the required system-level performance. They are specifically designed for ease of use and rapid system integration.

RT PolarFire devices have two types of user I/Os:

- General-purpose I/O (GPIO), which supports a wide range of I/O standards operating with supplies between 1.2 V to 3.3 V nominal.

- High-speed I/O (HSIO), which supports I/O standards operating with supplies between 1.2 V to 1.8 V.

For information about GPIO and HSIO performance specifications, see *RTPF FPGA Datasheet* (to be released).

GPIO and HSIO are organized in I/O banks and each I/O bank has dedicated I/O supplies. The unused supplies are connected to grounds to reduce noise leakage. In addition to GPIO and HSIO, a number of I/Os are associated with RT PolarFire FPGA system controller and with transceiver clocks and data pads. These I/Os are powered up independently of other user I/O banks. For more information, see RT PolarFire FPGA Transceiver User Guide (to be released), UG0714: PolarFire FPGA Programming User Guide, RT PolarFire FPGA Packaging and Pin Descriptions User Guide (to be released) and Package Pin Assignment Tables (PPATs).

This chapter describes the features and supported standards for each of these user I/O types, providing details about RT PolarFire FPGA I/O banks and I/O naming conventions.

#### 2.1 GPIO and HSIO Features

RT PolarFire devices support different I/O features for GPIO and HSIO. The following is a summary of I/O features:

#### 2.1.1 **GPIO Features**

- Supports 1.2 V to 3.3 V operation<sup>1</sup>

- · Single-ended input and output modes

- · Flexible supply voltage for certain I/O standards

- · Reference, differential, and complementary input receiver modes

- True current-based differential output driver modes and pseudo-differential complementary output modes

- Single-ended static or dynamic termination at 1.8 V and 1.5 V

- Differential static or dynamic termination of 100  $\Omega$

- · Cold-sparing and hot swapping (hot plug-in or hot-socket) capabilities

- Process, voltage, and temperature (PVT)-compensated programmable drive strengths

- Supports full and reduced drive for SSTL18 (as defined by JEDEC standards)

- Built-in weak pull-up, pull-down, and bus-keeper circuits

- Programmable hysteresis

- DDR3 support at up to 1.066 Gbps

#### 2.1.2 HSIO Features

- Supports 1.2 V to 1.8 V operation

- Single-ended input and output modes

- · Mixed single-ended input modes for LVTTL/LVCMOS, regardless of power supply level

- Reference, differential, and complementary input receiver modes

- Pseudo-differential complementary output modes

- Single-ended static or dynamic termination at 1.8 V, 1.5 V, 1.35 V, and 1.2 V

1.User should become familiar with single event latch-up risks in GPIO banks before selecting 2.5 V or 3.3 V I/Os. See *RT PolarFire Heavy Ion SEL Report*.

- PVT-compensated programmable drive strengths

- Supports full and reduced drives for SSTL18 as defined by JEDEC standards

- Built-in weak pull-up, pull-down, and bus-keeper circuits

- DDR3 and LPDDR3 supports at up to 1333 Mbps and DDR4 support at up to 1.6 Gbps

# 2.2 Supported I/O Standards

RT PolarFire FPGA GPIO and HSIO have configurable high-performance I/O drivers and receivers, supporting a wide variety of I/O standards.

The following table lists the I/O standards supported in the receiver and transmitter modes, respectively.

Table 1 • Supported I/O

| I/O Standards          | Receiver/Transmitter<br>Modes | V <sub>DDI</sub><br>(Nominal) Required | Bank Types | Applications                            |  |  |

|------------------------|-------------------------------|----------------------------------------|------------|-----------------------------------------|--|--|

| Single-Ended           | Single-Ended Standards        |                                        |            |                                         |  |  |

| PCI                    | Receiver, Transmitter         | 3.3 V                                  | GPIO       | PC and embedded systems                 |  |  |

| LVTTL <sup>1</sup>     | Receiver                      | 3.3 V, 2.5 V, 1.8 V,<br>1.5 V, 1.2 V   | GPIO       | General purpose                         |  |  |

|                        | Transmitter                   | 3.3 V                                  |            |                                         |  |  |

| LVCMOS33 <sup>1</sup>  | Receiver                      | 3.3 V, 2.5 V, 1.8 V,<br>1.5 V, 1.2 V   | GPIO       | General purpose                         |  |  |

|                        | Transmitter                   | 3.3 V                                  |            |                                         |  |  |

| LVCMOS25 <sup>1</sup>  | Receiver                      | 3.3 V, 2.5 V, 1.8 V,<br>1.5 V, 1.2 V   | GPIO       | General purpose                         |  |  |

|                        | Transmitter                   | 2.5 V                                  |            |                                         |  |  |

| LVCMOS18 <sup>1</sup>  | Receiver                      | 3.3 V, 2.5 V, 1.8 V,<br>1.5 V, 1.2 V   | GPIO, HSIO | General purpose                         |  |  |

|                        | Transmitter                   | 1.8 V                                  |            |                                         |  |  |

| LVCMOS15 <sup>1</sup>  | Receiver                      | 3.3 V, 2.5 V, 1.8 V,<br>1.5 V, 1.2 V   | GPIO, HSIO | General purpose                         |  |  |

|                        | Transmitter                   | 1.5 V                                  |            |                                         |  |  |

| LVCMOS12 <sup>1</sup>  | Receiver                      | 3.3 V, 2.5 V, 1.8 V,<br>1.5 V, 1.2 V   | GPIO, HSIO | General purpose                         |  |  |

|                        | Transmitter                   | 1.2 V                                  |            |                                         |  |  |

| SSTL25I,               | Receiver                      | 2.5 V                                  | GPIO       | DDR1 <sup>2</sup>                       |  |  |

| SSTL25II               | Transmitter                   | 2.5 V                                  | GPIO       | DDR1 <sup>2</sup>                       |  |  |

| SSTL18I,<br>SSTL18II   | Receiver, Transmitter         | 1.8 V                                  | GPIO, HSIO | DDR2 <sup>2</sup> /RLDRAM2 <sup>2</sup> |  |  |

| SSTL15I,<br>SSTL15II   | Receiver, Transmitter         | 1.5 V                                  | GPIO, HSIO | DDR3                                    |  |  |

| SSTL135I,<br>SSTL135II | Receiver, Transmitter         | 1.35 V                                 | HSIO       | DDR3L                                   |  |  |

| HSTL15I,<br>HSTL15II   | Receiver, Transmitter         | 1.5 V                                  | GPIO, HSIO | QDRII+                                  |  |  |

| HSTL135I,<br>HSTL135II | Receiver, Transmitter         | 1.35 V                                 | HSIO       | RLDRAM3 <sup>2</sup>                    |  |  |

| HSTL12I                | Receiver, Transmitter         | 1.2 V                                  | HSIO       | QDRII+                                  |  |  |

| -                      |                               |                                        |            |                                         |  |  |

Table 1 • Supported I/O (continued)

| I/O Standards           | Receiver/Transmitter<br>Modes | V <sub>DDI</sub><br>(Nominal) Required | Bank Types | Applications                 |

|-------------------------|-------------------------------|----------------------------------------|------------|------------------------------|

| HSUL18I,<br>HSUL18II    | Receiver, Transmitter         | 1.8 V                                  | GPIO, HSIO | LPDDR <sup>2</sup>           |

| HSUL12I,<br>HSUL12II    | Receiver, Transmitter         | 1.2 V                                  | HSIO       | LPDDR2 <sup>2</sup> , LPDDR3 |

| POD12I,<br>POD12II      | Receiver, Transmitter         | 1.2 V                                  | HSIO       | DDR4                         |

| Differential Sta        | andards                       |                                        |            |                              |

| LVDS33                  | Receiver                      | 3.3 V                                  | GPIO       | General purpose              |

|                         | Transmitter <sup>3</sup>      | 3.3 V                                  | GPIO       | General purpose              |

| LVDS25                  | Receiver                      | 2.5V                                   | GPIO       | General purpose              |

|                         | Transmitter <sup>3</sup>      | 2.5V                                   | GPIO       | General purpose              |

| LVDS18 <sup>4, 5</sup>  | Receiver                      | 1.8 V                                  | HSIO       | General purpose              |

| RSDS33                  | Receiver                      | 3.3 V                                  | GPIO       | General purpose              |

|                         | Transmitter <sup>3</sup>      | 3.3 V                                  | GPIO       | General purpose              |

| RSDS25                  | Receiver                      | 2.5 V                                  | GPIO       | General purpose              |

|                         | Transmitter <sup>3</sup>      | 2.5 V                                  | GPIO       | General purpose              |

| RSDS18 <sup>5</sup>     | Receiver                      | 1.8 V                                  | HSIO       | General purpose              |

| MINILVDS33              | Receiver                      | 3.3 V                                  | GPIO       | General purpose              |

|                         | Transmitter <sup>3</sup>      | 3.3 V                                  | GPIO       | General purpose              |

| MINILVDS25              | Receiver                      | 2.5V                                   | GPIO       | General purpose              |

|                         | Transmitter <sup>3</sup>      | 2.5V                                   | GPIO       | General purpose              |

| MINILVDS18 <sup>5</sup> | Receiver                      | 1.8 V                                  | HSIO       | General purpose              |

| SUBLVDS33               | Receiver                      | 3.3 V                                  | GPIO       | General purpose              |

|                         | Transmitter <sup>3</sup>      | 3.3 V                                  | GPIO       | General purpose              |

| SUBLVDS25               | Receiver                      | 2.5V                                   | GPIO       | General purpose              |

|                         | Transmitter <sup>3</sup>      | 2.5V                                   | GPIO       | General purpose              |

| SUBLVDS18 <sup>5</sup>  | Receiver                      | 1.8 V                                  | HSIO       | General purpose              |

| PPDS33                  | Receiver                      | 3.3 V                                  | GPIO       | General purpose              |

|                         | Transmitter <sup>3</sup>      | 3.3 V                                  | GPIO       | General purpose              |

| PPDS25                  | Receiver                      | 2.5 V                                  | GPIO       | General purpose              |

|                         | Transmitter <sup>3</sup>      | 2.5 V                                  | GPIO       | General purpose              |

| PPDS18 <sup>5</sup>     | Receiver                      | 1.8 V                                  | HSIO       | General purpose              |

| SLVS33                  | Receiver                      | 3.3 V                                  | GPIO       | General purpose              |

| SLVS25                  | Receiver                      | 2.5 V                                  | GPIO       | General purpose              |

| SLVS18                  | Receiver                      | 1.8 V                                  | HSIO       | General purpose              |

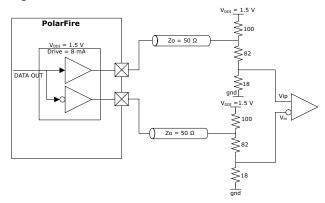

| SLVSE15 <sup>6</sup>    | Transmitter                   | 1.5 V                                  | GPIO, HSIO | General purpose              |

| HCSL33                  | Receiver                      | 3.3 V                                  | GPIO       | General purpose              |

| HCSL25                  | Receiver                      | 2.5 V                                  | GPIO       | General purpose              |

Table 1 • Supported I/O (continued)

| I/O Standards           | Receiver/Transmitter<br>Modes | V <sub>DDI</sub><br>(Nominal) Required | Bank Types | Applications                                     |

|-------------------------|-------------------------------|----------------------------------------|------------|--------------------------------------------------|

| HCSL18                  | Receiver                      | 1.8 V                                  | HSIO       | General purpose                                  |

| BUSLVDSE25 <sup>6</sup> | Transmitter                   | 2.5 V                                  | GPIO       | Multipoint backplane applications                |

| MLVDSE25 <sup>6</sup>   | Transmitter                   | 2.5 V                                  | GPIO       | Multipoint backplane applications                |

| LVPECL33                | Receiver                      | 3.3 V                                  | GPIO       | Video graphics and clock distribution            |

| LVPECLE33 <sup>6</sup>  | Transmitter                   | 3.3 V                                  | GPIO       | Video graphics and clock distribution            |

| MIPI25                  | Receiver                      | 2.5 V                                  | GPIO       | Consumer mobile applications                     |

| MIPIE25 <sup>6</sup>    | Transmitter                   | 2.5 V                                  | GPIO       | Consumer mobile applications,<br>High–speed Mode |

- Certain I/O standards are designed to support flexible V<sub>DDI</sub> assignment, see Mixed IO in VDDI Banks, page 22.

- 2. This application is supported by the I/O Standard, however, the RT PolarFire offering does not include the specific memory controller solution.

- 3. Buffers configured for these standards are true-differential transmitters that do not support bidirectional operations.

- 4. For HSIO, native LVDS inputs are supported with a single external-differential termination 100  $\Omega$  resistor, and LVDS transmit outputs are not supported in HSIO banks.

- These standards require an external voltage reference (V<sub>REF</sub>) and require two single-ended drivers with biasing through external resistors.

- 6. Buffers are configured as emulated-differential transmitters and also support bidirectional operations. However, they require an external board termination.

### 2.2.1 I/O Standard Descriptions

This section provides an overview for each of the I/O standards supported by RT PolarFire FPGA I/Os.

## 2.2.1.1 3.3 V Peripheral Component Interface (PCI)<sup>1</sup>

RT PolarFire FPGA GPIO supports the PCI I/O standards. The PCI standard uses an LVTTL input buffer and a push-pull output buffer. This standard is used for both 33 MHz and 66 MHz PCI bus applications.

# 2.2.1.2 Low-Voltage TTL (LVTTL)<sup>1</sup>

LVTTL is a general-purpose standard (EIA/JESD8-B) for 3.3 V applications. It uses an LVTTL input buffer and a push-pull output buffer. RT PolarFire FPGA GPIO supports the LVTTL I/O standards, and the LVTTL output buffer can have up to six different programmable drive strengths. For more information about programmable drive strength control, see Table 6, page 16.

#### 2.2.1.3 Low-Voltage CMOS (LVCMOS)

LVCMOS is a general-purpose standard implemented in CMOS transistors. RT PolarFire devices support five different LVCMOS operational modes:

- LVCMOS33<sup>1</sup>—an extension of the LVCMOS standard (JESD8-B-compliant) is used for general-purpose 3.3 V applications.

- LVCMOS25—an extension of the LVCMOS standard (JESD8-5-compliant) is used for general-purpose 2.5 V applications.

- LVCMOS18—an extension of the LVCMOS standard (JESD8-7-compliant) is used for general-purpose 1.8 V applications.

- LVCMOS15—an extension of the LVCMOS standard (JESD8-11-compliant) is used for general-purpose 1.5 V applications.

- LVCMOS12—an extension of the LVCMOS standard (JESD8-26-compliant) is used for general-purpose 1.2 V applications.

1.User should become familiar with single event latch-up risks in GPIO banks before selecting 2.5 V or 3.3 V I/Os. See *RT PolarFire Heavy Ion SEL Report*.

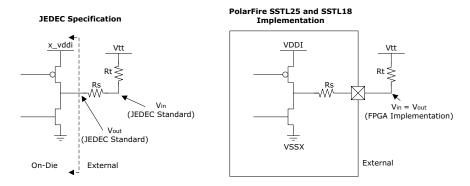

#### 2.2.1.4 Stub Series Terminated Logic (SSTL)

Stub series terminated logic (SSTL) is a general-purpose memory bus standard. RT PolarFire devices support the following SSTL operational modes:

- SSTL25I—SSTL Class I-standard with V<sub>DDI</sub> (nominal) = 2.5 V

- SSTL25II—SSTL Class II-standard with V<sub>DDI</sub> (nominal) = 2.5 V

- SSTL18I—SSTL Class I-standard with V<sub>DDI</sub> (nominal) = 1.8 V

- SSTL18II—SSTL Class II-standard with V<sub>DDI</sub> (nominal) = 1.8 V

- SSTL15I—SSTL Class I-standard with V<sub>DDI</sub> (nominal) = 1.5 V

- SSTL15II—SSTL Class II-standard with V<sub>DDI</sub> (nominal) = 1.5 V

- SSTL135I—SSTL Class I-standard with V<sub>DDI</sub> (nominal) = 1.35 V

- SSTL135II—SSTL Class II-standard with V<sub>DDI</sub> (nominal) = 1.35 V

SSTL25 is defined by the JEDEC standard, JESD8-9B, and used for DDR SDRAM and DDR1 memory interfaces. SSTL18 is defined by the JEDEC standard, JESD8, and used for DDR2 SDRAM memory interfaces. SSTL15 is used for DDR3 memory interfaces; SSTL135 is used for DDR3L memory interfaces.

For more information about signal levels for the various SSTL I/O standards, see RT PolarFire FPGA Datasheet (to be released).

#### 2.2.1.5 High-Speed Transceiver Logic (HSTL)

HSTL is a general-purpose, high-speed bus standard (EIA/JESD8-6) with a signaling range between 0 V and 1.5 V, and signals can either be single-ended or differential. This standard is used in memory bus interfaces with data switching capabilities of up to 1.267 GHz.

RT PolarFire devices support the following HSTL operational modes:

- HSTL15I—HSTL Class I-standard with V<sub>DDI</sub> (nominal) = 1.5 V

- HSTL15II—HSTL Class II-standard with V<sub>DDI</sub> (nominal) = 1.5 V

- HSTL135I—HSTL Class I-standard with V<sub>DDI</sub> (nominal) = 1.35 V

- HSTL135II—HSTL Class II-standard with V<sub>DDI</sub> (nominal) = 1.35 V

- HSTL12I—HSTL Class I-standard with V<sub>DDI</sub> (nominal) = 1.2 V

- HSTL12I—HSTL Class II-standard with V<sub>DDI</sub> (nominal) = 1.2 V

For more information about signal levels for the various HSTL I/O standards, see Table 1, page 3. also, see RT PolarFire FPGA Datasheet (to be released).

**Note:** HSTL135 and HSTL12 are not part of the JEDEC specification; they are scaled from HSTL15. For more information about HSTL signal levels, see *RT PolarFire FPGA Datasheet (to be released)*.

#### 2.2.1.6 High-Speed Unterminated Logic (HSUL)

HSUL, as specified by the JEDEC standard JESD8-22, is a standard for LPDDR2 and LPDDR3 memory buses. RT PolarFire devices support HSUL I/O standards in both HSIO and GPIO.

#### 2.2.1.7 Pseudo Open Drain (POD)

POD standards are intended for DDR4, DDR4L, and LLDRAM3 applications. RT PolarFire FPGA HSIO supports both POD receive and transmit modes.

#### 2.2.1.8 Low-Voltage Differential Signal (LVDS)

Low-voltage differential signaling (ANSI/TIA/EIA-644) is a high-speed, differential I/O standard. The voltage swing between two signal lines is approximately 350 mV. RT PolarFire FPGA GPIO supports LVDS receive and transmit modes. RT PolarFire FPGA HSIO supports LVDS receive mode with an external 100  $\Omega$  board termination, see I/O External Termination, page 24 for more information.

#### 2.2.1.9 Reduced-Swing Differential Signal (RSDS)

Reduced-swing differential signaling is similar to an LVDS high-speed interface using differential signaling, but with a smaller voltage swing and requiring a parallel termination resistor. RSDS is only intended for point-to-point applications. For more information about RSDS Voltage Swing, see *RT PolarFire FPGA Datasheet (to be released)*.

While RT PolarFire devices support RSDS receive and transmit modes with GPIO, RT PolarFire FPGA HSIO supports RSDS receive mode with an external 100  $\Omega$  on-board termination.

#### 2.2.1.10 Mini-LVDS

Mini-LVDS is a unidirectional interface from the timing controller to the column drivers in TFT LCD displays, and is specified in Texas Instruments standard, SLDA007A. RT PolarFire FPGA GPIO supports mini-LVDS in both receive and transmit modes. RT PolarFire FPGA HSIO supports mini-LVDS only in the receive mode and requires an external resistor..

#### 2.2.1.11 Sub-LVDS

Sub-LVDS is a differential low-voltage standard that is a subset of LVDS, and uses a reduced-voltage swing and lower common-mode voltage compared to LVDS. For sub-LVDS, the maximum differential swing is 200 mV compared to 350 mV for LVDS. The nominal common-mode voltage for sub-LVDS is 0.9 V, while it is 1.25 V for LVDS. RT PolarFire FPGA GPIO supports sub-LVDS in both receive and transmit modes. RT PolarFire FPGA HSIO supports sub-LVDS only in the receive mode and requires an external resistor.

#### 2.2.1.12 Point-to-Point Differential Signaling (PPDS)

PPDS is the next generation of the RSDS standards introduced by National Semiconductor Corporation, and is used to interface to next-generation LCD row and column drivers. PPDS inputs require a parallel termination resistor.

RT PolarFire FPGA GPIO supports PPDS in both receive and transmit modes. HSIO supports PPDS only in receive mode and requires an external resistor.

#### 2.2.1.13 Scalable Low-Voltage Signaling (SLVS)

SLVS is a chip-to-chip signaling standard designed for maximum performance with minimum power consumption, inheriting low noise susceptibility from LVDS. The standard features a scaled-down 400 mV signal swing, versus the 700 mV swing of LVDS, and includes a ground reference. RT PolarFire devices support the SLVS I/O standards in GPIO and HSIO banks, but an external resistor is required for transmitter mode. For more information, see Implementing Emulated Standards for Outputs, page 25.

#### 2.2.1.14 High-Speed Current Steering Logic (HCSL)

HCSL is a differential output standard used in PCI Express applications. Both GPIO and HSIO in RT PolarFire devices support the HCSL I/O standards (receive-only mode). Although, the common mode range for this standard is from 250 mV to 550 mV, RT PolarFire FPGA HCSL I/O receivers support a wider range of 50 mV to 2.4 V.

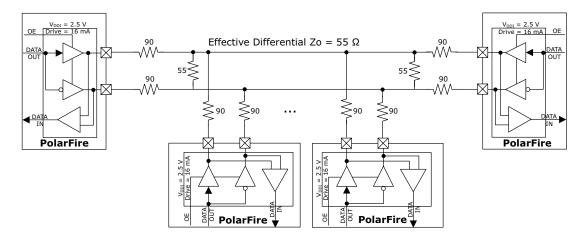

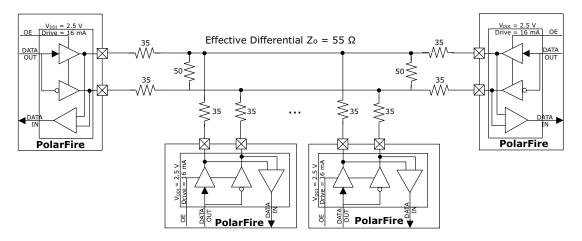

#### 2.2.1.15 Bus-LVDS (B-LVDS)/Multipoint LVDS (M-LVDS)

B-LVDS refers to bus interface circuits based on the LVDS technology with the M-LVDS specification extending the LVDS standard to high-performance multipoint bus applications. Multidrop and multipoint bus configurations may contain any combination of drivers, receivers, and transceivers. LVDS drivers provide the higher drive current required by B-LVDS and M-LVDS to accommodate bus loading. These drivers require series terminations for better signal quality and voltage swing control. The drivers can be located anywhere on the bus, and therefore termination is also required at both ends of the bus.

RT PolarFire FPGA GPIO supports B-LVDS and M-LVDS in receive mode. For transmit mode, however, external board termination is required. For more information about various BLVDS standards, see Bus-LVDS Emulated (BLVDSE25) Output Mode, page 26, and Multipoint Low-Voltage Emulated (MLVDSE25) Output Mode, page 26.

#### 2.2.1.16 Low-Voltage Positive Emitter-Coupled Logic (LVPECL)

LVPECL is a 3.3 V differential signal standard that transmits one data bit over a pair of signal lines, thus requiring two pins per input or output. The voltage swing between the two signal lines is approximately 850 mV. While LVPECL input is supported for RT PolarFire FPGA GPIO, external board termination is required for the LVPECL outputs. For more information about LVPECL33, see LVPECL Emulated (LVPECLE33) Output Mode, page 27.

# 2.2.1.17 Mobile Industry Processor Interface (MIPI) D-PHY

MIPI is a serial communication interface used in camera and display applications. RT PolarFire devices support implementing the MIPI D-PHY standards in GPIO bank using an external termination. For more information, see Implementing MIPI D-PHY, page 27.

## 2.3 I/O Banks

RT PolarFire device has eight user I/O banks. The I/O banks on the north side of the device support only HSIO. Each I/O bank has dedicated I/O supplies and grounds. Each I/O within a given bank shares the same  $V_{DDI}$  power supply, and the same  $V_{REF}$  reference voltage. Only compatible I/O standards can be assigned to a given I/O bank.

Each bank contains a bank power detector, and a bank receiver reference voltage generator to create an internally generated reference voltage, V<sub>REF</sub>. Each bank also interfaces with a PVT controller to calibrate the I/O buffer output driver strengths and termination values (needed only for certain I/O standards). The PVT controller generates a set of codes to control the source driver and the sink driver, and also calibrates the HSIO output slew. Each I/O buffer has individual drive-strength programmability to multiply the PVT digital code value by a drive setting to create the desired drive, impedance, or termination settings. For more information, see I/O Analog (IOA) Buffer Programmable Features, page 14.

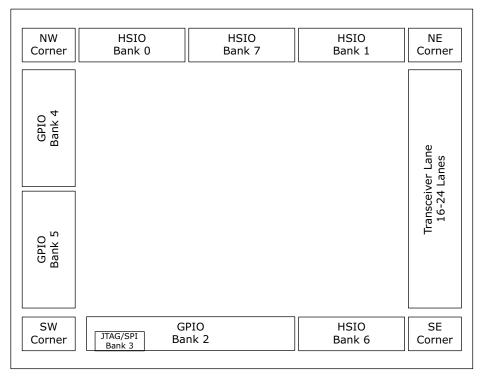

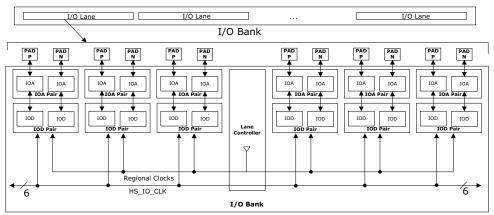

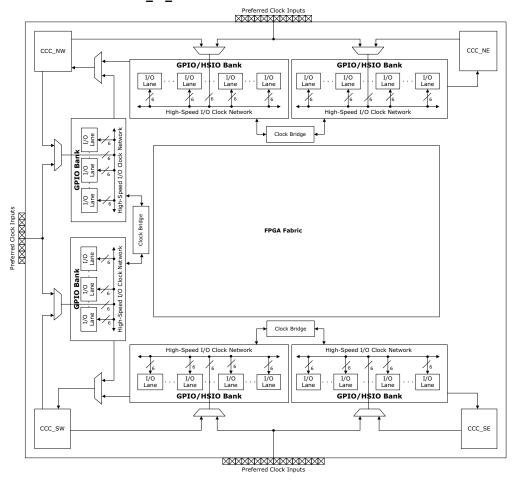

Figure 1, page 9 shows simplified RT PolarFire device floorplans for each device, including the bank locations. These figures also show the corner block and transceiver block. The corner block includes CCCs and two PLLs and two DLLs each, providing flexible clock management and synthesis for the FPGA fabric, external system, and I/Os. For more information about CCC and RT PolarFire FPGA transceivers, see *UG0684: PolarFire FPGA Clocking Resources User Guide* and *RT PolarFire FPGA Transceiver User Guide* (to be released).

Figure 1 • RTPF500T Device I/O Banks

# 2.4 Supply Voltages for RT PolarFire FPGA I/O Banks

RT PolarFire devices have multiple I/O banks that require the following bank power supplies listed in the table:

Table 2 • Supply Pin

| Name                | Description                                                                                                                                                                                                                                                                                                                     | Operating Voltage                                                                                                                                                     | Unused Condition                                                                                                                                                              |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DDIx</sub>   | Supply for I/O circuits in a bank                                                                                                                                                                                                                                                                                               | For JTAG bank—1.8 V/2.5<br>V/3.3 V<br>For GPIO bank—1.2 V/1.5 V/<br>1.8 V/2.5 V/3.3 V<br>For HSIO bank—1.2 V/1.5<br>V/1.8 V                                           | The bank supply is not allowed to be left floating for any unused bank. It must be powered down to ground by direct connection                                                |

| V <sub>DD25</sub>   | Power for corner PLLs and PNVM                                                                                                                                                                                                                                                                                                  | 2.5 V                                                                                                                                                                 | Must connect to 2.5 V                                                                                                                                                         |

| V <sub>DD18</sub>   | Power for programming and HSIO receiver                                                                                                                                                                                                                                                                                         | 1.8 V                                                                                                                                                                 | Must connect to 1.8 V                                                                                                                                                         |

| V <sub>DDAUXx</sub> | Auxiliary supply for I/O circuits. Auxiliary supply voltage must be set to 2.5 V or 3.3 V and must be always equal to or higher than V <sub>DDIx</sub> . See Table 14, page 23 GPIO Mixed Reference Receiver Mode for legal VDDI and VDDAUX combinations.                                                                       | Greater than or equal to V <sub>DDI</sub> . In cases where VDDI and VDDAUX in a given GPIO bank are both 2.5 V or 3.3 V, they should be tied together to same supply. | Must connect to greater than or equal to V <sub>DDI</sub>                                                                                                                     |

| V <sub>REF</sub>    | V <sub>REF</sub> is the supply reference voltage for reference receivers. Each bank can have only one V <sub>REF</sub> value. V <sub>REF</sub> can be externally supplied or internally generated, see Supply Voltages for RT PolarFire FPGA I/O Banks, page 10 for V <sub>REF</sub> assignment use model for more information. | Depends on the I/O standards                                                                                                                                          | The regular I/Os are used as V <sub>REF</sub> supply. Libero <sup>®</sup> configures unused user I/Os as input buffer disabled and output buffer tri-stated with weak pullup. |

# 2.5 RT PolarFire FPGA I/O Overview

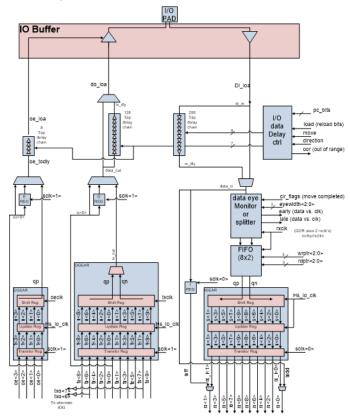

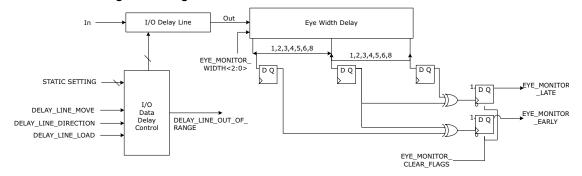

Each RT PolarFire FPGA I/O is composed of an analog I/O buffer (referred to as IOA) and a digital logic block (referred to as IOD). IOA blocks include analog input and output buffers, while IOD blocks include a logic that enables the IOA buffer to interface with the FPGA fabric. The IOD also includes data bus digital logic to widen the bus to and from the IOA, allowing the external pins to run at a much faster clock rate than the fabric logic.

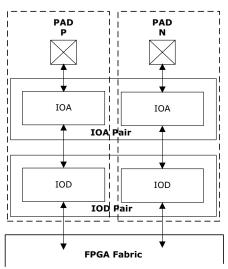

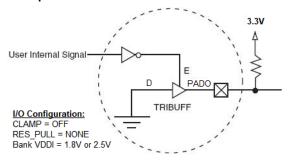

To support a variety of I/O standards, RT PolarFire FPGA I/Os are organized into pairs, as shown in the following illustration. The two I/O paths in a pair, labeled as positive (P) and negative (N) respectively, can be configured as two separate single-ended I/Os, as one differential, or as a complementary I/O pair.

Figure 2 • RT PolarFire FPGA I/O Pair

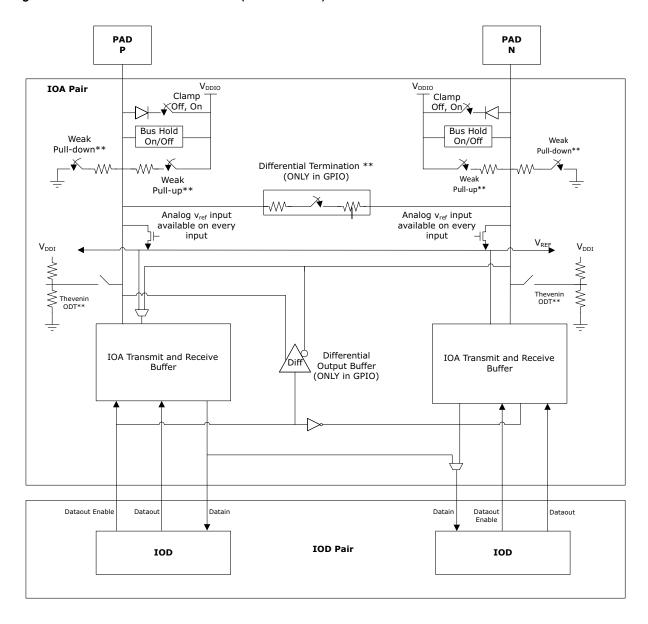

The IOA buffer includes a transmit and receive buffer, on-die termination (Thévenin, differential, up, and down), a slew-rate control circuit, a bus-keeper circuit, and a programmable weak pull-up or pull-down resistor. The transmit and receive buffers transfer signals between the I/O pad and the IOD. Figure 3, page 13 shows the overview of IOA buffer.

# 2.5.1 Single-Ended Transmitter and Receiver Mode

An I/O buffer can be configured as either a single-ended transmitter, a single-ended receiver, or both. RT PolarFire FPGA GPIO and HSIO both support single-ended mode.

#### 2.5.2 Differential Transmitter Mode

The I/O buffer pair allows implementing both true differential output mode and pseudo-differential output mode. The true differential output mode uses an LVDS H-bridge-type driver. The pseudo-differential output mode, also known as complementary-mode, consists of two single-ended drivers where one driver's output is inverted relative to the other. The pseudo-differential output drivers have lower signal integrity and performance, and usually require biasing by external resistors to emulate true differential signal levels. Only RT PolarFire FPGA GPIO bank supports true differential output modes using a differential current driver. Both, RT PolarFire FPGA GPIO and HSIO banks support complementary output modes.

#### 2.5.3 Differential Receiver Mode

Both GPIO and HSIO receivers support operations in differential receiver mode, where the input data from the differential pair of pads (PAD P and PAD N) is received on both pads and is then driven to the FPGA fabric from the IOD block on the P side.

Libero SoC controls the enabling and disabling of the transmit and receive buffer based upon the selected standard and I/O mode, whether single-ended or differential. For more information about IOA buffer and its use model, see I/O Features and Implementation, page 13.

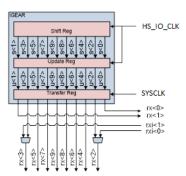

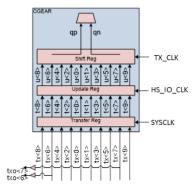

## 2.5.4 **I/O Digital (IOD)**

The IOD block interfaces with the FPGA fabric on one side and the IOA buffers on the other side, and deserializes and transfers input data to a lower core clock speed, or transfers lower-speed data from the fabric to the high-speed output clock domain, serializing it in the process. The RT PolarFire FPGA I/O digital block works in conjunction with fast and low-skew clock networks. It also includes special clock dividers and other support circuits to guarantee clock domain crossings. The I/O digital block deserializes high-speed DDR input data and transfers to FPGA fabric at lower speeds, and also serializes the lower speed FPGA fabric data and transfers to high-speed DDR output. For more information about IOD buffer and its use models, see IOD Features and User Modes, page 35.

#### 2.6 I/O Primitive

The RT PolarFire FPGA macro library includes a list of I/O primitives to support various I/O standards. Following are the generic I/O primitives, representing most of the available I/O standards.

- INBUF—represents input buffer

- INBUF\_DIFF—represents differential input buffer

- OUTBUF—represents output buffer

- · OUTBUF DIFF—represents differential output buffer

- TRIBUFF—represents tri-state buffer

- TRIBUFF\_DIFF—represents differential tri-state buffer

For more information about macro library, see PolarFire FPGA Macro Library User Guide.

# 3 I/O Features and Implementation

This chapter describes RT PolarFire FPGA I/O features and provides details about their use. It also provides guidelines for implementing the various I/O standards using RT PolarFire FPGA I/Os. Note that the terms receive and input, transmit and output are used interchangeably in this document.

The following illustration shows the RT PolarFire FPGA I/O pair block diagram.

Figure 3 • RT PolarFire FPGA I/O Pair (Detailed View)

**Note:** The weak pull-up, pull-down, and on-die termination (ODT) ranges are listed in *RT PolarFire FPGA Datasheet (to be released)*.

# 3.1 I/O Analog (IOA) Buffer Programmable Features

RT PolarFire FPGA GPIO and HSIO provide a number of programmable features. These features are set using the I/O attribute editor in Libero SoC, or through PDC commands. The following sections describe these features. For information about PDC constraints, see *PDC Commands User Guide for Libero SoC v12.4 for PolarFire*.

#### 3.1.1 Slew Rate Control

RT PolarFire FPGA GPIO supports slew rate control in non-differential output mode. Turning the slew rate on results in faster slew rate, which improves the available timing margin, see *RT PolarFire FPGA Datasheet (to be released)* for the timing data. When slew rate is turned off, the device uses the default slew rate to reduce the impact of simultaneous switching noise (SSN).

The following table lists the I/O standards that support slew rate control.

Table 3 • Slew Rate Control

| I/O Standards         | Supported I/O Type | Slew Rate Control Options |

|-----------------------|--------------------|---------------------------|

| PCI                   | GPIO (output only) | On (default),<br>Off      |

| LVTTL                 | GPIO (output only) | On (default),<br>Off      |

| LVCMOS25 and LVCMOS33 | GPIO (output only) | On (default),<br>Off      |

Slew rate settings are controlled using the I/O attribute editor in Libero SoC, or by using the following PDC command:

set\_io -slew <value>

The value can be set as on or off.

Slew rate control is not available in RT PolarFire FPGA HSIO buffers. However, these buffers have built-in PVT-compensated slew rate controllers for optimized signal integrity.

# 3.1.2 Programmable Weak Pull- Up/Down and Bus-Keeper (Hold) Circuits

RT PolarFire devices have a programmable weak pull-down (20  $\mathrm{K}\Omega$  typical), pull-up (20  $\mathrm{K}\Omega$  typical), and bus-keeper circuit on every I/O pad when in input and output mode. Weak pull-up and pull-down circuits create a default setting for an input when it is not driven. For outputs, the weak pull-up and weak pull-down can be optionally programmed to set an initial level on the output pad before being actively driven. The bus-keeper circuit is used to weakly hold the signal on an I/O pin at its last driven state, keeping it at a valid level with minimal power dissipation. The bus-keeper circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended oscillation. Differential inputs do not support the programmable weak pull-down, pull-up, and bus-keeper modes. An erased or blank device enables the weak pull-up resistor by default and tristate the output buffer. Unused I/O are programmed by default to enable the weak pull-up resistor and tristate the output buffer.

The following table lists the I/O standards that support weak pull- up/down and bus-keeper control.

Table 4 • Weak Pull and Bus-Keeper Control

| I/O Standards                                                  | Supported I/O<br>Types | Weak Pull and Bus-Keeper<br>Control Options         |

|----------------------------------------------------------------|------------------------|-----------------------------------------------------|

| LVTTL LVCMOS33, LVCMOS25, LVCMOS18, LVCMOS15, and LVCMOS12 PCI | GPIO (input only)      | Off<br>Weak pull-down<br>Weak pull-up<br>Bus-keeper |

| LVCMOS18, LVCMOS15, and LVCMOS12                               | HSIO (input only)      | Off<br>Weak pull-down<br>Weak pull-up<br>Bus-keeper |

The programmable weak pull-down, pull-up, and bus-keeper settings are controlled by using the I/O attribute editor in Libero SoC, or by using the following PDC command:

The value can be set as up, down, hold, or none.

# 3.1.3 Schmitt Trigger Input Hysteresis

RT PolarFire FPGA GPIO and HSIO can be configured as a Schmitt Trigger input that, when enabled, exhibits a hysteresis that helps to filter out the noise at the receiver and prevents double-glitching caused by noisy input edges.

The following table lists the I/O standards that support the Schmitt Trigger feature. For more information about hysteresis values for different I/O standards when Schmitt Trigger mode is enabled, see *RT PolarFire FPGA Datasheet (to be released)*.

Table 5 • Schmitt Trigger Control

| I/O Standards                        | Supported I/O Types | Schmitt Trigger Control Options |

|--------------------------------------|---------------------|---------------------------------|

| LVTTL<br>LVCMOS33<br>LVCMOS25<br>PCI | GPIO (input only)   | On<br>Off                       |

| LVCMOSI15<br>LVCMOSI18               | HSIO (input only)   | On<br>Off                       |

Schmitt Trigger mode is enabled by using the I/O attribute editor in Libero SoC, or by using the following PDC command:

set\_io -schmitt\_trigger <value>

The value can be set as on or off.

# 3.1.4 Programmable Output Drive Strength

For LVCMOS, LVTTL, LVDS, and PPDS I/O standards, the RT PolarFire FPGA I/O output buffer has programmable drive strength control to mitigate the effects of high signal attenuation caused by long transmission lines.

The following table lists the programmable drive strength support and settings in RT PolarFire devices.

Table 6 • Programmable Drive Strength Control

| Supported I/O Types         | Drive Strength Settings (mA)                                                                                                                                                                                                        |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO (output only)          | 2, 4, 8, 12, 16, 20                                                                                                                                                                                                                 |

| GPIO (output only)          | 2, 4, 8, 12, 16, 20                                                                                                                                                                                                                 |

| GPIO (output only)          | 2, 4, 6, 8, 12, 16                                                                                                                                                                                                                  |

| GPIO (output only)          | 3, 3.5, 4, 6 <sup>1</sup>                                                                                                                                                                                                           |

| GPIO (output only)          | 1.5, 2, 3                                                                                                                                                                                                                           |

| GPIO (output only)          | 3, 3.5, 4, 6                                                                                                                                                                                                                        |

| GPIO (output only)          | 1, 1.5, 2                                                                                                                                                                                                                           |

| GPIO (output only)          | 1.5, 2, 3                                                                                                                                                                                                                           |

| GPIO and HSIO (output only) | 2, 4, 6, 8, 10, 12                                                                                                                                                                                                                  |

| GPIO and HSIO (output only) | 2, 4, 6, 8, 10                                                                                                                                                                                                                      |

| GPIO and HSIO (output only) | 2, 4, 6, 8, 10                                                                                                                                                                                                                      |

|                             | GPIO (output only)  GPIO and HSIO (output only) |

<sup>1.</sup> Recommendation to use 100  $\Omega$  source termination with 6 mA LVDS output drive strength, that is, SOURCE TERM = 100 when OUT DRIVE = 6.

The programmable drive strength is set by using the I/O attribute editor in Libero SoC or by using the following PDC command:

Values can be set as listed in Table 6, page 16.

# 3.1.5 Programmable Output Impedance Control

For voltage reference I/O standards, RT PolarFire FPGA I/Os provide the option to control the driver impedance for certain I/O standards: SSTL, HSUL, HSTL, POD, and LVSTL.

The following table lists the programmable output impedance support and settings in RT PolarFire devices.

Table 7 • Programmable Output Impedance Standards

| I/O Standards | Supported I/O Types | Impedance (Ω)   |

|---------------|---------------------|-----------------|

| SSTL25I       | GPIO                | 48, 60, 80, 120 |

| SSTL25II      | GPIO                | 34, 40, 48, 60  |

| SSTL18I       | GPIO and HSIO       | 40, 48, 60, 80  |

| SSTL18II      | GPIO and HSIO       | 30, 34, 40, 48  |

| SSTL15I       | GPIO and HSIO       | 40, 48          |

| SSTL15II      | GPIO and HSIO       | 27, 30, 34      |

| SSTL135I      | HSIO                | 40, 48          |

| SSTL135II     | HSIO                | 27, 30, 34      |

| HSUL18I       | GPIO and HSIO       | 34, 40, 55, 60  |

| HSUL18II      | GPIO and HSIO       | 22, 25, 27, 30  |

|               |                     |                 |

<sup>2.</sup> LVCMOS12 output drive strength of 10 mA is supported only for HSIO.

Table 7 • Programmable Output Impedance Standards (continued)

| I/O Standards | Supported I/O Types | Impedance (Ω)                    |

|---------------|---------------------|----------------------------------|

| HSTL15I       | GPIO and HSIO       | 34, 40, 50, 60                   |

| HSTL15II      | GPIO and HSIO       | 22, 25, 27, 30                   |

| HSTL135I      | HSIO                | 34, 40, 50, 60                   |

| HSTL135II     | HSIO                | 22, 25, 27, 30                   |

| HSUL12I       | HSIO                | 34, 40, 48, 60, 80, 120          |

| POD12I        | HSIO                | 40, 48, 60                       |

| POD12II       | HSIO                | 27, 30, 34                       |

| LVSTLI        | HSIO                | 30, 34, 40, 48, 60, 80, 120, 240 |

| LVSTLII       | HSIO                | 30, 34, 40, 48, 60, 80, 120, 240 |

The output impedance values can be programmed by using the I/O attribute editor in Libero SoC, or by using the following PDC command:

set\_io -impedance <value>

values can be set as listed in Table 7, page 16.

#### 3.1.6 Differential Near End Termination

Programmable output termination is provided for many differential output types. By default, applications with differential signaling is terminated at the receiver (or far-end). However, near-end or source termination can be used to improve signal integrity in lossy connections.

Table 8 • Source Termination Support

| I/O Standard                                              | Values                       |

|-----------------------------------------------------------|------------------------------|

| LVDS25, LVDS33, MINILVDS25, MINILVDS33, LCMDS33, LCMDS25, | OFF, 100. The default is OFF |

| PPDS25, PPDS33, RSDS25, RSDS33, SUBLVDS25, SUBLVDS331     |                              |

The source termination values can be programmed by using the I/O attribute editor in Libero SoC, or by using the following PDC command:

[-SOURCE TERM <value>]

# 3.1.7 On-Die Termination (ODT)

ODT is used to terminate input signals, helping to maintain signal quality, saving board space, and reducing external component costs. In RT PolarFire FPGAs, ODT is available in receive mode and also in bidirectional mode when the I/O acts as an input. If ODT is not used or not available, the RT PolarFire FPGA I/O standards may require external termination for better signal integrity. For more information, see I/O External Termination, page 24.

ODT can be a pull-up, pull-down, differential, or Thévenin termination with both static and dynamic control available, and is set by using the I/O attribute editor in Libero SoC or by using a PDC command.

The following table lists ODT support in RT PolarFire devices.

Table 9 • ODT Support in GPIO and HSIO

| I/O Standards                                                                                                    | I/O Types<br>(Input Only) | ODT Control          | ODT Type                      | ODT (Ω)                  |

|------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------|-------------------------------|--------------------------|

| LVDS33, LVDS25<br>RSDS33, RSDS25,<br>MINILVDS33,<br>MINILVDS25,<br>SUBLVDS33,<br>SUBLVDS25,<br>LVPECL33,LVPECL25 | GPIO, HSIO                | Off<br>On<br>Dynamic | Off<br>Differential           | 100                      |

| SSTL18I, SSTL18II                                                                                                | GPIO, HSIO                | Off<br>On<br>Dynamic | Off<br>Thévenin               | 50, 75, 150              |

| SSTL15I, SST15II                                                                                                 | GPIO, HSIO                | Off<br>On<br>Dynamic | Off<br>Thévenin               | 20, 30, 40, 60, 120      |

| SSTL135I, SSTL135II                                                                                              | HSIO                      | Off<br>On<br>Dynamic | Off<br>Thévenin               | 20, 30, 40, 60, 120      |

| POD12I, POD12II                                                                                                  | HSIO                      | Off<br>On<br>Dynamic | Off<br>Up                     | 34, 40, 48, 60, 120, 240 |

| HSUL12I, HSUL12II                                                                                                | HSIO                      | Off<br>On<br>Dynamic | Off<br>Up                     | 120, 240                 |

| HSTL15I, HSTL15II                                                                                                | GPIO                      | Off<br>On<br>Dynamic | Off<br>Differential           | 50                       |

| HSUL18I, HSUL18II                                                                                                | GPIO, HSIO                | Off<br>On<br>Dynamic | Off<br>Differential           | 50                       |

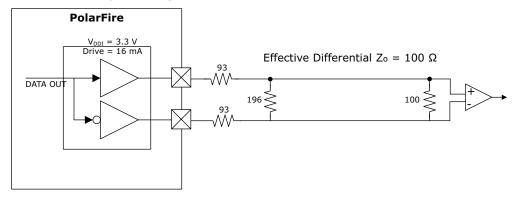

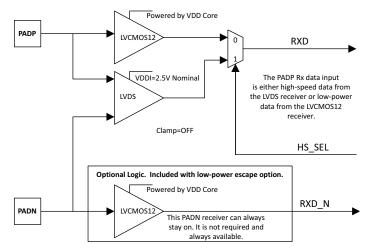

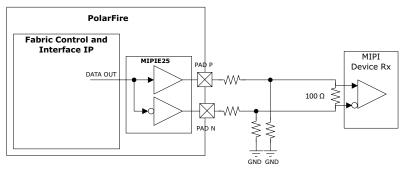

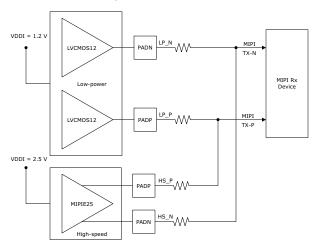

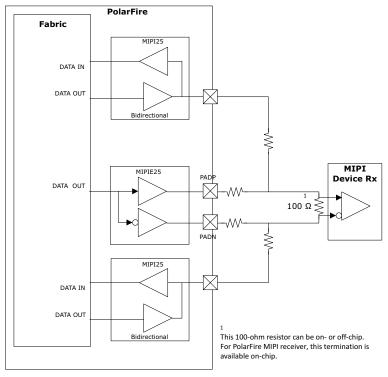

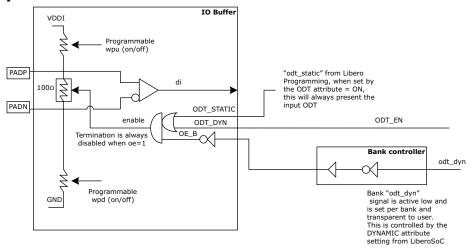

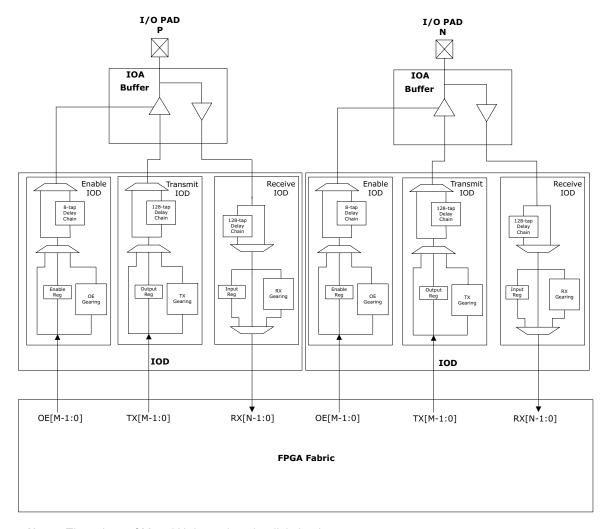

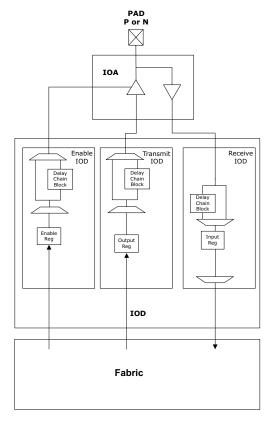

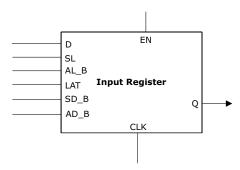

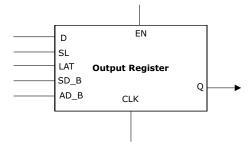

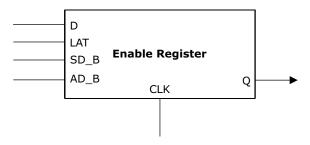

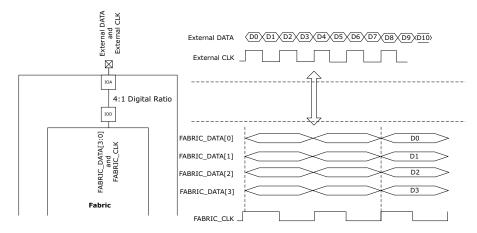

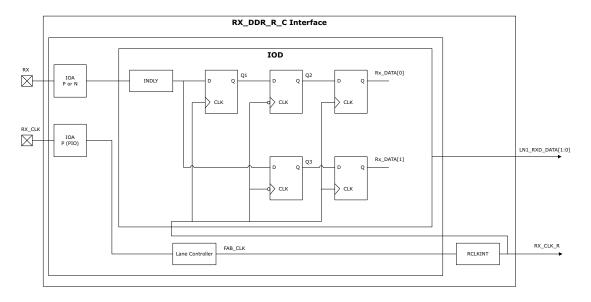

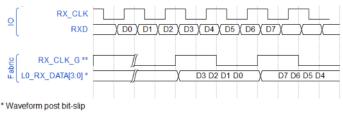

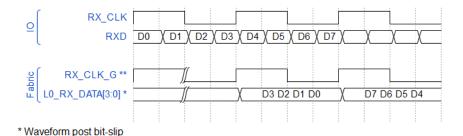

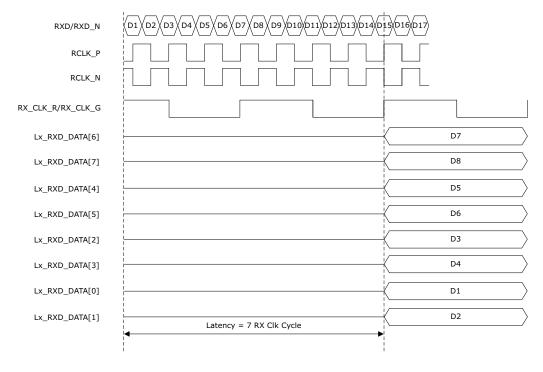

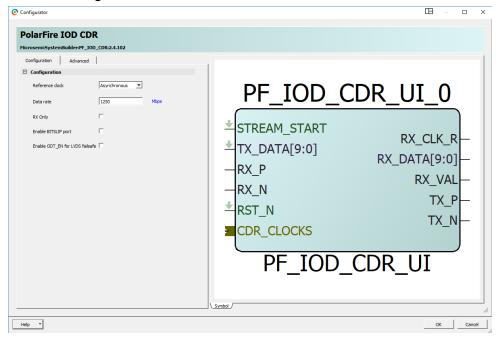

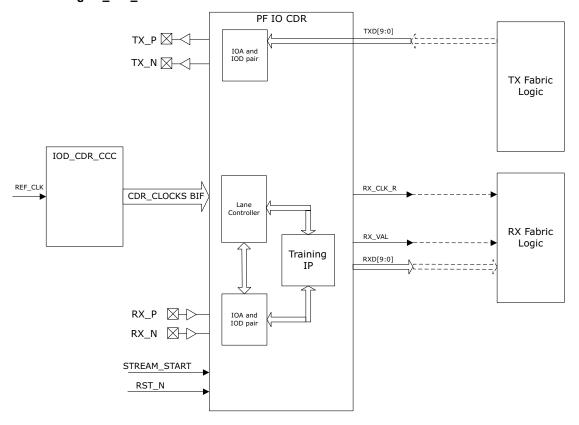

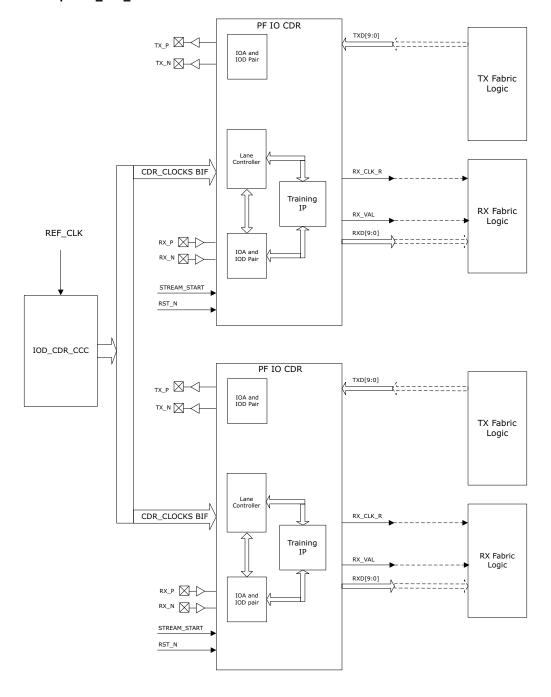

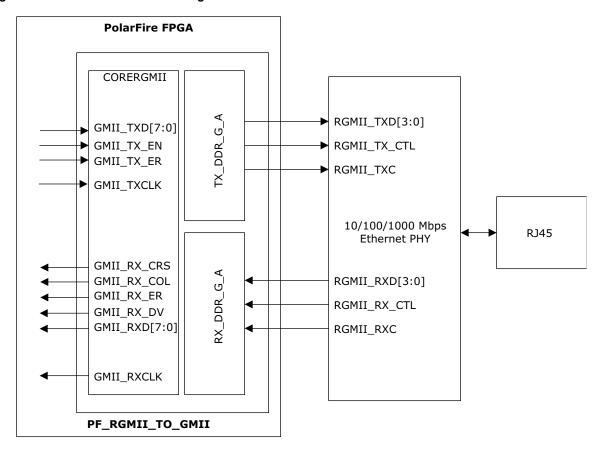

| LVCMOS25                                                                                                         | GPIO, HSIO                | Off<br>On            | Off<br>Down                   | 120, 240                 |