# Microsemi SoftConsole v6.5 Release Notes

# **Table of Contents**

| Table of Conten      | ts                                    | 2  |

|----------------------|---------------------------------------|----|

| Microsemi SoftC      | Console v6.5                          | 7  |

| Introduction         |                                       | 7  |

| Overview             |                                       | 7  |

| New in v6.5          |                                       | 7  |

| New in v6.4          |                                       | 8  |

| Key features         |                                       | 8  |

| Features not support | ted                                   | 8  |

| Quick start guide    |                                       | 9  |

| Supported platfo     | orms                                  | 11 |

| Free/Open source     | ce packages                           | 12 |

|                      |                                       |    |

| Installation         |                                       | 18 |

| Windows              |                                       | 18 |

| Insta                | alling                                | 18 |

| Linux                |                                       | 18 |

| Insta                | alling                                | 18 |

| Post                 | t installation steps                  | 19 |

|                      | emi Tools/Resources                   |    |

| Libero SoC/Firmware  | e Catalog                             | 24 |

| Firmware drivers     |                                       | 24 |

|                      | dware Abstraction Layers              |    |

|                      | pheral firmware drivers               |    |

|                      | ching firmware to the target hardware |    |

|                      | rammer                                |    |

| Microsemi's GitHub   | repositories                          | 25 |

| •                    |                                       |    |

|                      |                                       |    |

|                      | mple projects                         |    |

|                      | mple debug launch configurations      |    |

|                      |                                       |    |

| Creating a new work  | space                                 | 27 |

|                      |                                       |    |

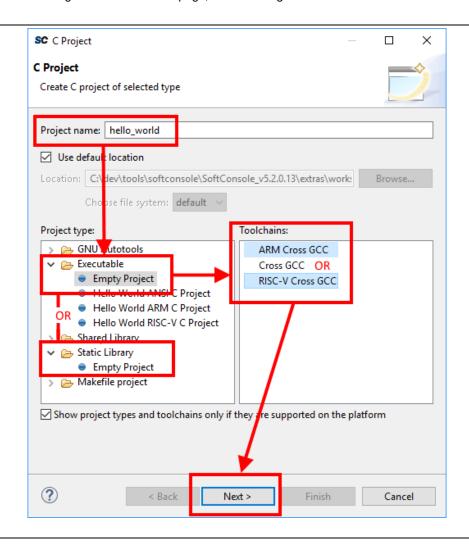

| Creating a new proje | ect                                   | 28 |

| Project Settings                                                                                                           | 29       |

|----------------------------------------------------------------------------------------------------------------------------|----------|

| All CPU targets                                                                                                            | 29       |

| RISC-V targets                                                                                                             | 32       |

| Cortex-M targets                                                                                                           | 32       |

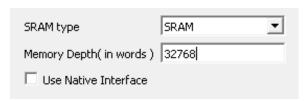

| SmartFusion2 Cortex-M3 and RTG4/SmartFusion2/IGLOO2/PolarFire RISC-V targ                                                  | gets. 33 |

| For demonstration a SmartFusion2 was chosen, however similar steps can be appall other targets and other types of memories |          |

| Adding source files to a project                                                                                           | 34       |

| Building a project                                                                                                         | 34       |

| Debension                                                                                                                  | ٥٢       |

| Debugging                                                                                                                  |          |

| Debug launch configurations                                                                                                |          |

| OpenOCD command line options and scripts                                                                                   |          |

| SmartFusion/SmartFusion2 DEVICE                                                                                            |          |

| Board scripts                                                                                                              |          |

| Cortex-M1 Board Script                                                                                                     | 42       |

| FlashPro JTAG speed                                                                                                        | 43       |

| Other OpenOCD options                                                                                                      | 43       |

| SoftConsole OpenOCD script parameters                                                                                      | 43       |

| Board configuration for FlashPro debugging                                                                                 | 43       |

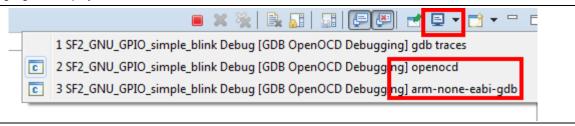

| Using a debug session                                                                                                      |          |

| Launching a debug session                                                                                                  |          |

| Memory Monitor                                                                                                             |          |

| Console view                                                                                                               |          |

| Built-in serial terminal view                                                                                              |          |

| Debug using a specific FlashPro programmer                                                                                 |          |

| Debugging using a non FlashPro JTAG interface                                                                              |          |

| How to connect to/debug a running program                                                                                  |          |

| Troubleshooting                                                                                                            |          |

|                                                                                                                            |          |

| Renode emulation platform                                                                                                  |          |

| Multi-hart debugging                                                                                                       |          |

| Call stack and conditional breakpoints                                                                                     |          |

| Macros                                                                                                                     |          |

| Symbols and simple trace functionality                                                                                     |          |

| Creating bridge/tunnel to the emulation                                                                                    |          |

| Using Wireshark to monitor the network traffic inside the emulation                                                        | 59       |

| Emulation time                                                                                                             | 60       |

| Tweaking the emulation performance                                                                                         | 61       |

| Web content of the mpfs-freertos-lwip example                                                                              | 62       |

| Tips, tricks, and issues                                                                                                   | 63       |

| Using Open Source Software tool such as Renode will contaminate my proprietary                                             |          |

| There was an error executing command 'sysbus.cpu StartGdbServer 3333 true'                                                 |          |

| Wireshark constantly shows dialog about unsaved packets                                                                    |          |

| Wireshark shows a significant amount of traffic and overloads my target                                                    |          |

| "Could not set TUNSETIFF, error: 2"                                             | 64 |

|---------------------------------------------------------------------------------|----|

| How do I delete Renode's bridge TAP networking interface?                       | 64 |

| Can't see the interface after invoking BridgeNetworkMac0 macro                  | 64 |

| Can't ping my target                                                            | 64 |

| My target doesn't respond to packets                                            | 65 |

| Other Factories                                                                 | 00 |

| Other Features                                                                  |    |

| Cortex-M semi-hosting                                                           |    |

| Integer only newlib support                                                     |    |

| Static stack profiling                                                          |    |

| Cppcheck                                                                        | 68 |

| Known Issues and useful tips                                                    | 69 |

| Reset/power cycle the target hardware before each RISC-V debug session          | 69 |

| Debug launch configuration settings differ for Cortex-M and RISC-V              | 69 |

| RISC-V memory view problems                                                     |    |

| Memory Monitor fails to display                                                 | 69 |

| Windows occasionally crashes when plugging FlashPro in/out                      | 69 |

| OpenOCD crashes when attempting to debug RISC-V                                 |    |

| RISC-V C++ support                                                              | 70 |

| FlashPro programmers cannot be shared by applications                           | 70 |

| Initial startup may be slow                                                     | 70 |

| Flash Programming                                                               | 70 |

| Build Project context menu option sometimes disabled                            | 70 |

| Windows firewall                                                                | 70 |

| Multiple debug sessions                                                         | 70 |

| FlashPro JTAG debugging is unreliable on virtual machines                       | 70 |

| "DAP transaction stalled (WAIT)" messages when debugging SmartFusion2 Cortex-M3 | 70 |

| "Error: Got exception" when reading some RISC-V registers                       |    |

| OpenOCD error/info messages when debugging RISC-V                               |    |

| Debugging and multiple device JTAG chains                                       |    |

| RISC-V target support                                                           | 72 |

| SoftConsole v3.4 or earlier workspaces/projects                                 | 72 |

| SoftConsole v5.0 RISC-V projects and debug launch configurations                | 72 |

| SmartFusion2 DPK unlocking                                                      |    |

| CMSIS needs environment variable                                                | 75 |

| FTDI detected as ttyUSB on Linux                                                | 75 |

| Program file does not exist                                                     | 76 |

| Target emulation `elf64-littleriscv' does not match `elf32-littleriscv'         | 76 |

| sprint()/scanf() print empty characters instead of floating point number digits | 77 |

| Error message: can't link hard-float modules with soft-float modules            |    |

| Multiple definition of `_start'/`_init'/`_fini' etc                             |    |

| Undefined reference to `printf'/`puts'/`write'/`strlen' etc                     |    |

| Route printf() output to UART                                                   | 77 |

| Program image is too large                                                      | 78 |

| cc1: error: requested ARI requires -march to subsume the 'D' extension          |    |

| undefined reference to `stack_top' etc                                                            | 79 |

|---------------------------------------------------------------------------------------------------|----|

| After duplication of the project (copy/paste) debugging no longer works                           | 79 |

| Progam has exited with code:0x00000003 (got into a trap exception)                                | 80 |

| Size optimizations cause trap exception: Load/Store address misaligned (mcause 4/6)               | 82 |

| <bul><li><built-in>: internal compiler error: Illegal instruction</built-in></li></bul>           |    |

| (Renode:5523): GLib-CRITICAL $^{**}$ : Source ID 13802 was not found when attempting to remove it |    |

| /riscv_hal/entry.S:113: Error: Instruction csrr requires absolute expression                      | 82 |

| Connecting to remote OpenOCD                                                                      | 82 |

| Glitches, unstable UI and cosmetic issues on Linux                                                |    |

| Debugger Console View is not working or GDB is misbehaving                                        |    |

| Build fails when using "Print removed sections (-Xlinkerprint-gc-sections)"                       | 83 |

| Debug launcher fails with "Error: gdb sent a packet with wrong register size"                     |    |

| Debug launcher is not connecting to ARM target                                                    |    |

| Application traps at random places or even before reaching main                                   |    |

| Running SoftConsole from command line                                                             |    |

| Invalid project path: Duplicate path entries found Warnings                                       |    |

| Application is stuck in main_first_hart and is not reaching e51()                                 |    |

| "No installed packages"                                                                           |    |

| Tab with an error message is opened before breaking into the main function                        |    |

| What are the Robot references in SoftConsole?                                                     |    |

| "cc1.exe: error: -march= <your_architecture> invalid ISA string"</your_architecture>              |    |

| "cc1.exe: error: requested ABI requires -march to subsume the 'D' extension"                      |    |

| "cc1: error: rv32e requires ilp32e ABI"                                                           |    |

| "target emulation `elf64-littleriscv' does not match `elf32-littleriscv'"                         |    |

| Deeply nested code causes crashes and glitches                                                    |    |

| Renode on startup crashes with an unhandled exception                                             | 87 |

| Other useful Documentation                                                                        | 88 |

| Product Support                                                                                   | 89 |

|                                                                                                   | 05 |

| Customer Service                                                                                  | 89 |

| Customer Technical Support Center                                                                 | 90 |

| Customer Technical Support Center                                                                 | 09 |

| Technical Support                                                                                 | 89 |

| Website                                                                                           | 89 |

| Contacting the Customer Technical Support Center                                                  | ۵n |

| Email                                                                                             |    |

| My Cases                                                                                          |    |

| Outside the U.S.                                                                                  |    |

| Outside the 0.5                                                                                   | 90 |

| ITAR Technical Support                                                                            | 90 |

# Introduction

These are release notes for Microsemi SoftConsole v6.5.

This document uses <SoftConsole-install-dir> as a placeholder for the actual SoftConsole install directory. Where this is mentioned substitute the actual SoftConsole install directory name (e.g.

C:\Microchip\SoftConsole\_v6.5 on Windows or \$HOME/Microsemi\_SoftConsole\_v6.5 on Linux).

# Overview

# New in v6.5

• Support for PolarFire SoC Icicle board's Embedded FlashPro6 Rev B for debugging a PolarFire SoC MSS (Microcontroller Sybsystem) RISC-V multicore core complex based SoC.

Important note: The Icicle board's Embedded FlashPro6 programmer must be upgraded from Rev A to Rev B for it to work with SoftConsole. Refer to the Libero SoC v12.5 SP1 or Program Debug Tools v12.5 SP1 release notes for details of how to upgrade the Embedded FlashPro6 from Rev A to Rev B.

The following table summarizes the FlashPro support in SoftConsole v6.5:

| FlashPro → Supports?↓                                                      | FlashPro3/LCPS<br>(standalone &<br>embedded) | FlashPro4<br>(standalone &<br>embedded) | FlashPro5<br>(standalone &<br>embedded) | FlashPro6 | Embedded<br>FlashPro6 Rev<br>B | Embedded<br>FlashPro6 Rev<br>A |

|----------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------|-----------------------------------------|-----------|--------------------------------|--------------------------------|

| Windows?                                                                   | X                                            | X                                       | Υ                                       | Υ         | Υ                              | N                              |

| Linux?                                                                     | N                                            | N                                       | Y                                       | Υ         | Y                              | N                              |

| Virtual<br>Machine?                                                        | N                                            | N                                       | N                                       | N         | N                              | N                              |

| Mi-V RV32<br>RISC-V soft<br>core debug via<br>UJTAG                        | Y                                            | Y                                       | Y                                       | N         | N                              | N                              |

| Mi-V RV32<br>RISC-V soft<br>core debug via<br>JTAG signals<br>on I/O pins? | Y                                            | Y                                       | Y                                       | Y         | N                              | N                              |

| Cortex-M1 soft core debug via UJTAG?                                       | Y                                            | Y                                       | Y                                       | N         | N                              | N                              |

| Cortex-M1 soft core debug via                                              | Y                                            | Υ                                       | Υ                                       | Υ         | N                              | N                              |

| JTAG signals on I/O pins?                 |   |   |   |   |   |   |

|-------------------------------------------|---|---|---|---|---|---|

| PolarFire SoC<br>UltraSoC<br>trace/debug? | Y | Y | Y | Υ | N | N |

# New in v6.4

PolarFire SoC boot mode 0/1 programming support – please refer to <SoftConsole-installdir>/extras/mpfs/readme.txt for full details.

# **Key features**

- Runs on Windows and Linux.

- Development/debug support for Microsemi PolarFire SoC RISC-V 64-bit multi-processor, Microsemi Mi-V RISC-V and Arm® Cortex®-M CPUs/SoCs.

- Built using the latest industry standard stock free/open source components and tools for Arm® Cortex®-M and RISC-V firmware development, debugging and emulation.

- Support for Microsemi PolarFire SoC, Microsemi SmartFusion<sup>®</sup> and SmartFusion2 Arm<sup>®</sup> Cortex-M3,

Microsemi Arm<sup>®</sup> Cortex-M1 and Microsemi Mi-V RISC-V firmware development, debugging and emulation.

- Uses OpenOCD for Arm Cortex-M and RISC-V debugging and SmartFusion/SmartFusion2/Fusion eNVM programming/program download.

- Supports download to and debugging from SmartFusion eSRAM and eNVM, SmartFusion2 eSRAM, eNVM and external RAM (MDDR), Cortex-M1 RAM and Fusion eNVM, and RISC-V RAM.

- Supports FlashPro JTAG programmer for debugging (FlashPro3/4/5/6 on Windows, FlashPro5/6 on Linux).

- Supports Arm Cortex-M semi-hosting redirection of standard/file I/O from target board to host debugger.

- Includes Antmicro's Renode emulation platform which can be used to emulate PolarFire SoC and Mi-V hardware targets allowing development/debugging of software for these targets even when hardware is not available.

- Includes a built-in terminal emulator for connecting to a target board's serial port or the host OS's command shell

- Includes cppcheck and companion cppcheclipse plugin integration for static code analysis.

- Supports newlib nano for Cortex-M and RISC-V providing an even more lightweight standard library implementation ideal for resource constrained environments.

- Suitable for development, debug and emulation of bare metal and lightweight RTOS based embedded applications.

# Features not supported

- Some PolarFire SoC features are not supported in this release but will be added in v6.5.

- Workspaces, projects and debug launch configurations from some earlier SoftConsole releases are not compatible with SoftConsole v6.5

- Workspaces and projects created with SoftConsole releases prior to v4.0 are not compatible and must be recreated.

- RISC-V projects created with SoftConsole v5.1 or earlier are not compatible and must be recreated.

- Renode debug launch configurations/launch groups for RISC-V created with SoftConsole v6.0 or earlier are not compatible and must be recreated.

- In general, it is recommended that any existing workspace, project and debug launch configuration/group be recreated based on the SoftConsole v6.5 example workspace, projects and debug launch configurations/groups and reviewed to ensure that all configuration settings are appropriate.

- Debugging a CoreJTAGDebug/UJTAG Cortex-M1 or Mi-V RISC-V CPU that is in one device in a multiple device JTAG chain.

- Debugger driven download of programs to non-CFI external parallel flash memories.

- SoftConsole does not support or work on any 32-bit Windows or Linux operating system.

- Core8051/Core8051s firmware development and debugging. Use Keil C51 Development Tools with Core8051/Core8051s ISD-51 support.

# **Quick start guide**

- 1. It is strongly recommended to read the Installation section of Release Notes before the installation as there might be extra manual steps required (especially on Linux).

- 2. Download the SoftConsole installer from the Microsemi website. Verify the downloaded file integrity using the checksum file provided.

- 3. Follow the installation instructions below for the relevant OS platform. If installing on Linux pay careful attention to the pre-install and post-install instructions.

- 4. Run SoftConsole from the desktop shortcut or "Start" menu entries created by the installer. This will launch SoftConsole and open the example workspace.

- Note: Do not launch the eclipse.exe binary directly as SoftConsole requires certain environment variables to be set up locally to function properly. Instead run SoftConsole using the provided scripts softconsole.cmd on Windows and softconsole.sh on Linux.

- 5. Do not use custom workspaces or workspaces from previous SoftConsole releases. Use the bundled workspaces, either workspace.examples which has bundled examples or workspace.empty which is empty has no imported projects. If a new workspace is required then copy and rename workspace.empty.

- Sharing/copying workspaces between machines or OSs is inadvisable and may lead to problems.

- 6. The project settings must match the target hardware (and your Libero design) to use the projects on an actual board.

- If the example project is very different from the target hardware, then generate relevant HAL/CMSIS and firmware drivers from Libero, the Firmware Catalog or the PolarFire SoC Bare Metal Library Bitbucket repository and copy the generated files into the project replacing the existing files which were targeting the original hardware. Make sure that configuration details such as clock speeds are matched in the firmware project and the target hardware.

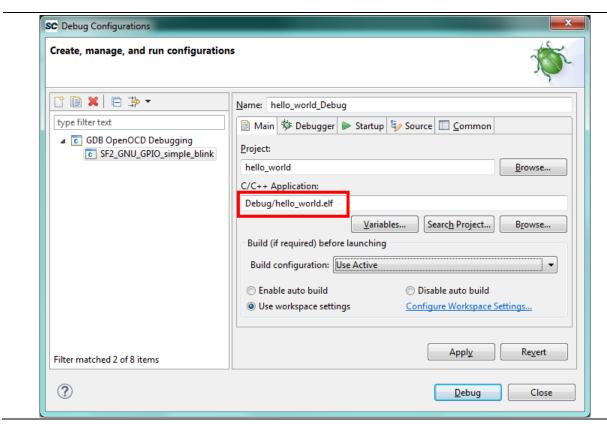

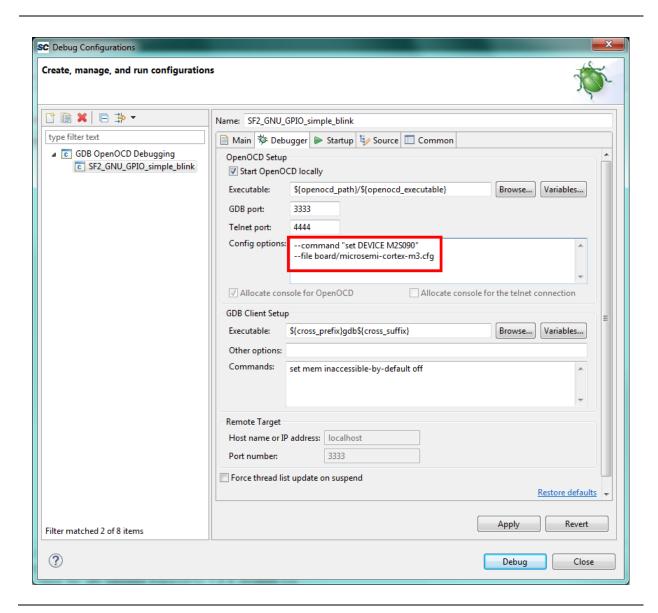

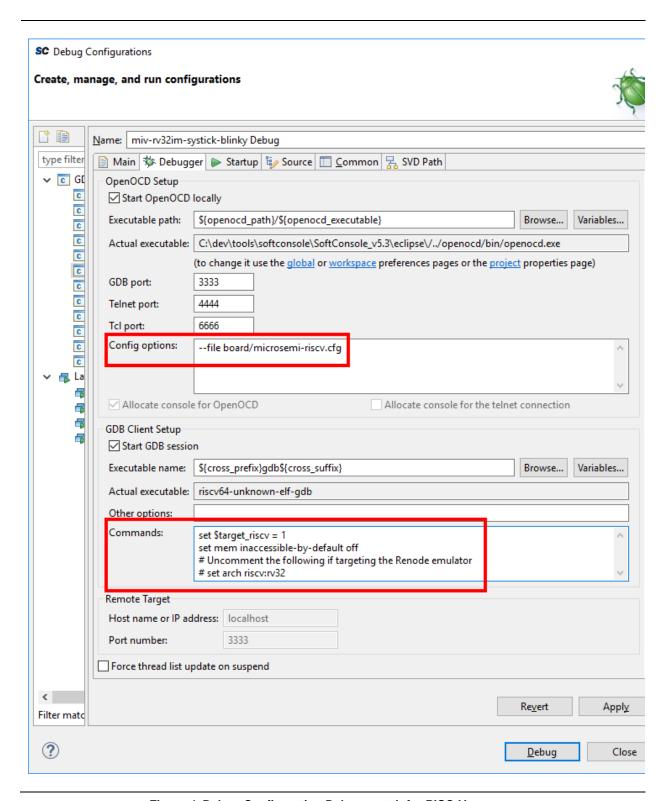

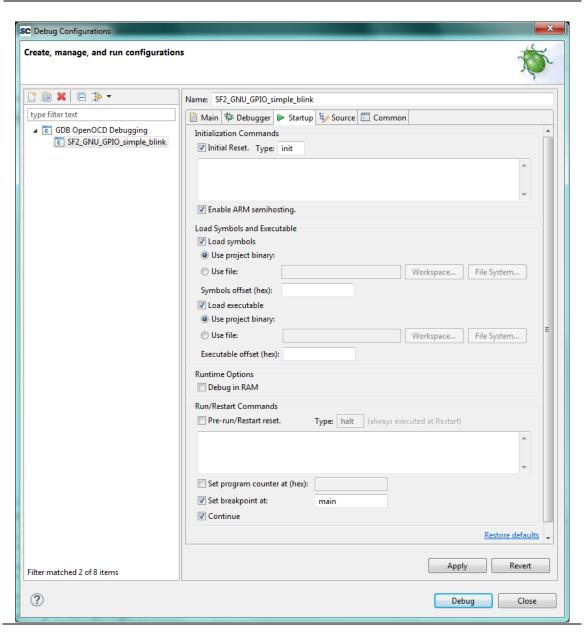

- 7. The example projects come with default debug launch configurations for debugging. If necessary, modify the settings passed to OpenOCD so that they match the actual target hardware. In some cases, these changes can be as minor as changing set DEVICE M2S090 to set DEVICE M2S025 in the debug launcher to target the M2S025 devices.

- 8. Use the Microsemi website (https://www.microsemi.com/product-directory/product-support/4217-fpgas-socs-support), Firmware Catalog (https://www.microsemi.com/products/fpga-soc/design-resources/design-software/firmware-catalog), the Microsemi GitHub (https://github.com/RISCV-on-Microsemi-FPGA) and/or the PolarFire SoC Bare Metal Library Bitbucket repository (https://bitbucket.microchip.com/projects/FPGA\_PFSOC\_ES/repos/polarfire-soc-bare-metal-library) to obtain example/demo/reference Libero designs and SoftConsole projects. See also the bundled examples in the workspace.examples for simple illustrative examples.

9. It is recommended to read the release notes in full as the document describes the correct way of using SoftConsole, ways to avoid problems and describes the known issues and ways to address them. When troubleshooting an issue, copy the error (or a part of the error) and search for it the Release Notes, the sections contain the error messages to make their solutions easier to find.

# Supported platforms

· Operating systems - 64bit only

NOTE: physical machines only recommended/supported - see the Known Issues section for details of issues with virtual machines.

- Windows

- •

- **8.1**

- 10

- Linux

- CentOS and Red Hat Enterprise Linux (RHEL)

- 7

- Ubuntu

- 16.04 LTS

- openSUSE

- LEAP 15

- Debian

- 9

#### CPUs

- o Microsemi PolarFire SoC RISC-V 64-bit multi-processor FPGA

- o Microsemi Mi-V RISC-V CPU soft cores for PolarFire, RTG4, IGLOO2 and SmartFusion2 FPGAs

- Microsemi SmartFusion2 Arm Cortex-M3

- Microsemi SmartFusion Arm Cortex-M3

- Microsemi Arm Cortex-M1 for RTG4 and PolarFire FPGAs

- Microsemi Arm Cortex-M1 for M1 IGLOO, ProASIC3, ProASIC3L and Fusion FPGAs

# JTAG Debug

- Microsemi FlashPro3, FlashPro4, FlashPro5 and FlashPro6 (standalone only not embedded) on Windows

- Microsemi FlashPro5 and FlashPro6 (standalone only, not embedded) on Linux

- Olimex ARM-USB-TINY-H

- Other JTAG debug probes supported by OpenOCD may be used but are not specifically tested or supported

## Other software

- o Microsemi Libero SoC

- Microsemi Libero SoC v12.5 SP1

- Microsemi Firmware Catalog v12.5 SP1

- o Firmware (minimum required version)

- PolarFire SoC PSE\_HAL 1.5.107

- RISC-V Hardware Abstraction Layer (HAL) 3.0.105

- SmartFusion2 CMSIS Hardware Abstraction Layer 2.3.105

- SmartFusion CMSIS-PAL 2.4.102

- Cortex-M1 CMSIS Hardware Abstraction Layer 2.0.105

- (DirectCore) Hardware Abstraction Layer 2.3.103

# Free/Open source packages

# Packages used

Microsemi SoftConsole uses several, mostly free and/or open source, packages. Microsemi acknowledges and thanks those organization, communities and individual developers who work on these projects and make them available to others for reuse under the relevant license conditions.

|               | Java runtime                                                                                                                                                                                                                                                             |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Version       | OpenJDK 8u252                                                                                                                                                                                                                                                            |  |  |

| Home page     | https://openjdk.java.net/                                                                                                                                                                                                                                                |  |  |

| Documentation | https://openjdk.java.net/faq/                                                                                                                                                                                                                                            |  |  |

| License       | GPL v2 with the Classpath Exception                                                                                                                                                                                                                                      |  |  |

|               | https://openjdk.java.net/legal/                                                                                                                                                                                                                                          |  |  |

| Notes         | OpenJDK provides the base Java platform on which Eclipse/CDT and other Eclipse plugins run.                                                                                                                                                                              |  |  |

|               | Credit/thanks to Oracle and the OpenJDK open source development community.                                                                                                                                                                                               |  |  |

|               | Eclipse/CDT                                                                                                                                                                                                                                                              |  |  |

| Version       | Eclipse 4.15 2020-03 (SimRel) + CDT 9.11                                                                                                                                                                                                                                 |  |  |

| Home page     | https://www.eclipse.org/downloads/packages/release/2020-03/r                                                                                                                                                                                                             |  |  |

|               | https://projects.eclipse.org/projects/tools.cdt/releases/9.11.0                                                                                                                                                                                                          |  |  |

| Documentation | https://help.eclipse.org/2020-03/index.jsp                                                                                                                                                                                                                               |  |  |

| License       | Eclipse Public License v2.0                                                                                                                                                                                                                                              |  |  |

|               | https://www.eclipse.org/legal/epl-2.0/                                                                                                                                                                                                                                   |  |  |

| Notes         | Eclipse/CDT – in conjunction with the GNU MCU Eclipse plugins – provide the main SoftConsole GUI/IDE (Graphical User Interface/Integrated Development Environment).                                                                                                      |  |  |

|               | The Windows Eclipse/CDT starter.exe has been modified by Microchip to allow for graceful termination of OpenOCD or other external executables launched from Eclipse.                                                                                                     |  |  |

|               | SoftConsole builds from the Eclipse Platform Runtime Binary (PRB) package and only adds those plugins that are absolutely necessary for Microchip target development/debug to avoid unnecessary bloat. Users can still install any additional plugins that they see fit. |  |  |

|               | Credit/thanks to the Eclipse/CDT developer community.                                                                                                                                                                                                                    |  |  |

|               | GNU MCU Eclipse Plugins                                                                                                                                                                                                                                                  |  |  |

| Version       | v4.7.1-201911052135 (https://gnu-mcu-eclipse.github.io/blog/2019/11/06/plugins-v4.7.1-201911052135-released/)                                                                                                                                                            |  |  |

| Home page     | https://gnu-mcu-eclipse.github.io/                                                                                                                                                                                                                                       |  |  |

| Documentation | https://gnu-mcu-eclipse.github.io/                                                                                                                                                                                                                                       |  |  |

| License       | Eclipse Public License v1.0                                                                                                                                                                                                                                              |  |  |

|               | https://gnu-mcu-eclipse.github.io/licenses/plug-ins/#eclipse-public-license                                                                                                                                                                                              |  |  |

|               | The copyright owner for all the GNU MCU Eclipse plug-ins is Liviu Ionescu and all rights are reserved.                                                                                                                                                                   |  |  |

| Notes         | Only the following GNU MCU Eclipse plugins are used:                                                                                                                                                                                                                     |  |  |

|               | <ul> <li>GNU MCU C/C++ Arm Cross Compiler: provides specific support for Arm targets by way of custom project properties pages and integration with the back-end GNU Arm Embedded Toolchain.</li> <li>GNU MCU C/C++ RISC-V Cross Compiler: provides specific support for RISC-V targets by way of custom project properties pages and integration with the back end RISC-V GNU Toolchain.</li> <li>GNU MCU C/C++ OpenOCD Debugging: provides specific support for debugging Arm and RISC-V targets using OpenOCD from within the Eclipse environment.</li> <li>Credit/thanks to Liviu Ionescu and the GNU MCU Eclipse project and development community.</li> </ul> |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | GNU Arm Embedded GCC Toolchain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Version       | xPack GNU Arm Embedded GCC toolchain v9.2.1-1.1-20191025 build based on GNU Arm Embedded Toolchain 9-2019-q4-major (https://developer.arm.com/tools-and-software/open-source-software/developer-tools/gnu-toolchain/gnu-rm/downloads)                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Home page     | https://xpack.github.io/arm-none-eabi-gcc/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Documentation | https://developer.arm.com/open-source/gnu-toolchain/gnu-rm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| License       | https://launchpad.net/gcc-arm-embedded/5.0/5-2016-q3-update/+download/license.txt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Notes         | Provides GCC, GDB, binutils, newlib (including newlib-nano) etc. development/debug tools for Arm targets (in particular Cortex-M targets).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|               | Details of the specific versions of the individual tools in each release package can be found on the Arm Developer website.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|               | SoftConsole bundles the xPack GNU Arm Embedded GCC build of the GNU Arm Embedded Toolchain because it offers more cross platform (especially Linux) portability than the Arm build of the same tools and also Windows 64-bit builds (Arm currently provide only 32-bit builds for Windows).                                                                                                                                                                                                                                                                                                                                                                         |

|               | Credit/thanks to Arm and the GNU Arm Embedded Toolchain development community and Liviu Ionescu and the xPack and GNU MCU Eclipse projects and development communities.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|               | Arm Cortex Microcontroller Software Interface Standard (CMSIS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Version       | V4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Home page     | https://www.arm.com/products/processors/cortex-m/cortex-microcontroller-software-interface-standard.php                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Documentation | http://www.keil.com/pack/doc/CMSIS/General/html/index.html                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| License       | Apache 2.0 License: http://www.keil.com/pack/doc/CMSIS/General/html/index.html#License                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Notes         | Along with the Microsemi SmartFusion2 CMSIS Hardware Abstraction Layer and SmartFusion CMSIS-PAL firmware packages provides a lightweight hardware abstraction layer on which startup code and firmware drivers can operate.  Credit/thanks to Arm.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               | GNU RISC-V Embedded GCC Toolchain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Version       | xPack GNU RISC-V Embedded GCC toolchain v8.3.0-1.1 build with additional multilibs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Home page     | https://xpack.github.io/riscv-none-embed-gcc/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Documentation | https://xpack.github.io/riscv-none-embed-gcc/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| License       | https://github.com/riscv/riscv-gnu-toolchain/blob/master/LICENSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### Notes

The riscv64-unknown-elf prefixed tools support 32-bit and 64-bit targets and multilibs for all architectures ("native" abi only) excluding any E architectures.

Slightly modified versions of the xPack GNU RISC-V Embedded GCC build scripts (https://xpack.github.io/riscv-none-embed-gcc/) are used to build the SoftConsole GNU RISC-V Embedded GCC Toolchain.

Multilibs are provided for the following RISC-V arch (architecture) and abi tuples:

- march=rv32i/mabi=ilp32

- march=rv32ia/mabi=ilp32

- march=rv32iac/mabi=ilp32

- march=rv32iaf/mabi=ilp32f

- march=rv32iafc/mabi=ilp32f

- march=rv32ic/mabi=ilp32

- march=rv32if/mabi=ilp32f

- march=rv32ifc/mabi=ilp32f

- march=rv32im/mabi=ilp32

- march=rv32ima/mabi=ilp32

- march=rv32imac/mabi=ilp32

- march=rv32imaf/mabi=ilp32f

- march=rv32imafc/mabi=ilp32f

- march=rv32imc/mabi=ilp32march=rv32imf/mabi=ilp32f

- march=rv32imfc/mabi=ilp32f

- march=rv64i/mabi=lp64

- march=rv64ia/mabi=lp64

- march=rv64iac/mabi=lp64

- march=rv64iaf/mabi=lp64f

- march=rv64iafc/mabi=lp64f

- march=rv64iafd/mabi=lp64d

- march=rv64iafdc/mabi=lp64d

- march=rv64ic/mabi=lp64

- march=rv64if/mabi=lp64f

- march=rv64ifc/mabi=lp64f

- march=rv64ifd/mabi=lp64d

- march=rv64ifdc/mabi=lp64d

- march=rv64im/mabi=lp64

- march=rv64ima/mabi=lp64

- march=rv64imac/mabi=lp64

- march=rv64imaf/mabi=lp64f

- march=rv64imafc/mabi=lp64f

- march=rv64imafd/mabi=lp64d

- march=rv64imafdc/mabi=lp64d

- march=rv64imc/mabi=lp64

- march=rv64imf/mabi=lp64fmarch=rv64imfc/mabi=lp64f

- march=rv64imfd/mabi=lp64d

- march=rv64imfdc/mabi=lp64d

This is a full list of supported multilibs. Arch/abi tuples not listed are not supported. This includes all RV32E targets.

Note that this suite of multilibs supports the "natural" ABI for each architecture. If an RV64G (rv64imafd or more specifically rv64imafdZicsr\_Zifencei) architecture is chosen, but not the natural ABI lp64f (natural would be in this case lp64d), then the resulting multilib is not supported. However, choosing the rv64imaf with its natural ABI lp64f will work. Instead of selecting architecture and then ABI a reversed approach might be

|               | better. Select an ABI to fulfil application's requirements and then the select the minimal architecture that can handle that given ABI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | The "default/native" mode of the tools is RV64GC in the absence of any -march/-mabi flags being passed to the tools.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               | Credit/thanks to the RISC-V development community and Liviu Ionescu and the xPack and GNU MCU Eclipse projects and development communities.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|               | OpenOCD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Version       | v0.10.0+dev based on the SiFive fork of OpenOCD with additional SoftConsole and UltraSoC mods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Home page     | http://openocd.org/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Documentation | http://openocd.org/documentation/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| License       | GNU General Public License v2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               | https://www.gnu.org/licenses/old-licenses/gpl-2.0.en.html                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Notes         | OpenOCD sits between GDB and the target hardware (JTAG debug probe, target board and CPU) to allow for program download and debug using real hardware. When debugging Eclipse launches GDB and then uses GDB's GDB/MI (Machine Interface) to communicate with the debugger. Meanwhile GDB communicates with OpenOCD using OpenOCD's Remote Serial Protocol interface. GDB debug operations are translated into JTAG operations by OpenOCD which communicates with the target hardware/CPU using JTAG via the relevant JTAG debug probe. OpenOCD also has knowledge of specific CPU target debug frameworks (e.g. Arm CoreSight, RISC-V Debug Modules v0.11 and v0.13 – https://github.com/riscv/riscv-debug-spec) so that it can communicate with and debug supported RISC-V CPUs.  SoftConsole OpenOCD is based on the SiFive fork of OpenOCD (https://github.com/riscv/riscv-openocd) with additional SoftConsole modifications to add support for FlashPro, SmartFusion2/SmartFusion/Fusion eNVM, finding scripts relative to OpenOCD bin directory, other fixes and enhancements.  It is also built using some UltraSoC mods to support UltraDevelop trace functionality. SoftConsole's version of OpenOCD is built using slightly modified versions of the xPack OpenOCD (https://xpack.github.io/openocd/) build scripts |

|               | Credit/thanks to the OpenOCD development community, SiFive, UltraSoC and Liviu Ionescu and the xPack and GNU MCU Eclipse projects and development communities.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               | GNU MCU Eclipse Build Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Version       | v2.12-20190422                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               | https://gnu-mcu-eclipse.github.io/windows-build-tools/releases/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Home page     | https://gnu-mcu-eclipse.github.io/windows-build-tools/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Documentation | https://gnu-mcu-eclipse.github.io/windows-build-tools/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

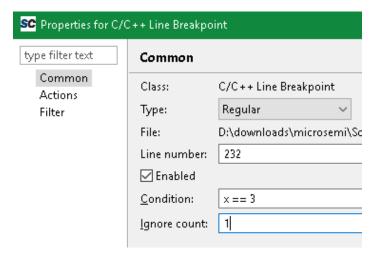

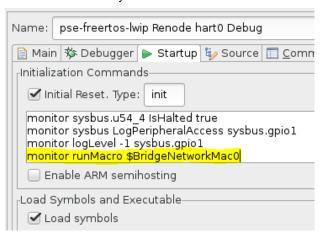

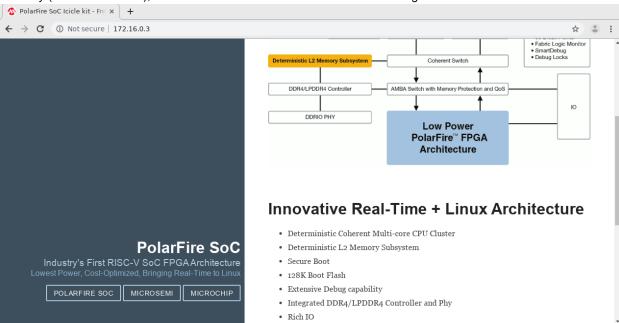

| License       | https://gnu-mcu-eclipse.github.io/licenses/tools/ make: GNU General Public License v3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |