Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

COMPANY CONFIDENTIAL

# Introduction

The following document provides guidelines for designing a PoE system Powered Device (PD) compliant with IEEE 802.3af (IEEE802.3at Type 1) or 802.3at (Type 2) standards by using Microsemi's PD70101 or PD70201 PD Front End and PWM Controller ICs. The PD70101 and PD70201 ICs are integrated POE Powered Device (PD) Front end and PWM controller for IEEE 802.3af and IEEE 802.3at applications, respectively. The Front End section of the PD70101 IC provides all necessary detection, classification, and operating current levels compliant with the IEEE 802.3af PoE standard. The Front end section of the PD70201 IC provides the necessary detection, classification, 2-event mark for "AT" flag, and operating current levels compliant with the IEEE 802.3at Type 2 standard. The PWM controller section of both PD70101 and PD70201 ICs integrate all functions necessary to provide a complete DC/DC solution for both isolated and non-isolated application requirements.

This document includes a brief overview of PoE functionality with respect to the applicable standards; however it is not to be considered a substitute for the IEEE standards. The applicable standard should always be consulted when making decisions affecting the design of the circuit.

# Applicable Documents

- IEEE 802.3af-2003 standard, DTE Power via MDI

- IEEE802.3at-2009 standard, DTE Power via MDI

- Microsemi Application Note AN193, Designing a type1/2 IEEE 802.3af/at Powered Device Using PD70100/PD70200 Front End ICs, catalogue number 06-0129-080

- PD70101/PD70201 datasheet, catalogue number 06-0132-058

## **POE Overview**

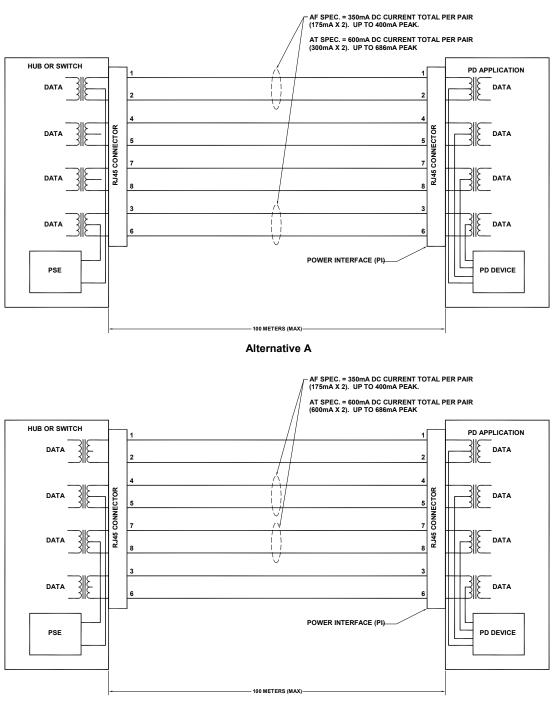

In its simplest form, PoE consists of a power source, referred to as Power Source Equipment (PSE), an Ethernet cable (typically contained in an infrastructure) with maximum length of 100 meters, and a Powered Device (PD) which accepts both data and power from the Power Interface (PI) of the Ethernet cable. The PI is typically an eight pin RJ45 type connector. Per IEEE 802.3at specification, power may be transmitted on one set of 2-pair combinations, designated "Alternate A" or Alternate B". A diagram of this arrangement is shown in Figure 1.

IEEE 802.3af or IEEE 802.3at type 1 PSEs are designed to operate with Ethernet cabling which may include CAT3 (per TIA/EIA 568). As such they may contain 26AWG wire. A cable of this type may impose a 20Ω maximum power loop resistance to a PSE operating into the maximum specified 100 meter cable length. IEEE 802.3at type 2 PSEs are designed to operate at higher output power levels with CAT 5 or higher (per TIA/EIA 568) Ethernet cabling. These cables contain 24AWG wire (or better) and may impose a maximum  $12.5\Omega$  power loop resistance to a PSE operating into the maximum specified 100 meter cable length. The voltage drop and internal temperature rise created in a 100 meter Ethernet cable affect the voltage and current available to the PD. A brief comparison between the AF and AT standards for the PSE and the PD are presented in Tables 1 and 2, respectively.

In addition to IEEE 802.3af/at specifications, a compatible PSE may transmit power over all 4 pairs for additional power available to the PD application.

For further information regarding POE please consult Microsemi Application Note AN193, Designing a type1/2 IEEE 802.3af/at Powered Device Using PD70100/PD70200 Front End ICs, catalogue number 06-0129-080.

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

COMPANY CONFIDENTIAL

Alternative B

Figure 1: Basic PoE Configuration for IEEE 802.3at Standard

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

#### COMPANY CONFIDENTIAL

| Comparison of IEEE 802.3af and IEEE 802.3at Standards for PSE |                                                                 |                                                                    |  |

|---------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|--|

| PSE Requirements                                              | IEEE 802.3af or IEEE<br>802.3at type 1                          | IEEE 802.3at type 2                                                |  |

| Guaranteed Power at PSE Output                                | 15.4W                                                           | 30W                                                                |  |

| PSE Output Voltage                                            | 44V to 57V                                                      | 50V to 57V                                                         |  |

| Guaranteed Current at PSE Output                              | 350mA DC with up to<br>400mA peaks                              | 600mA DC with up to<br>686mA peaks                                 |  |

| Maximum Cable Resistance                                      | 20Ω                                                             | 12.5Ω                                                              |  |

| Physical Layer Classification                                 | Optional                                                        | Mandatory                                                          |  |

| Supported Physical Layer Classification<br>Classes            | Class 0 to Class 3                                              | Class 4 - mandatory                                                |  |

| Data Link Classification                                      | Optional                                                        | Mandatory                                                          |  |

| 2-Events Classification                                       | Not required                                                    | Mandatory                                                          |  |

| 4 pairs power feeding                                         | Not allowed                                                     | Allowed with 2 collocated<br>PSEs                                  |  |

| Communication Supported                                       | 10/100 BASE-T<br>(Midspans)<br>10/100/1000 BASE-T<br>(switches) | 10/100/1000 BASE-T<br>Including Midspans (Both<br>type1 and type2) |  |

Table 1: IEEE 802.3af and 802.3at Standards for PSE

| Comparison of IEEE 802.3af and IEEE 802.3at Standards for PD |                                                                 |                                                                    |  |

|--------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|--|

| PD Requirements                                              | IEEE 802.3af or IEEE<br>802.3at type 1                          | IEEE 802.3at type 2                                                |  |

| Guaranteed Power at PD Input                                 | 12.95W                                                          | 25.50W                                                             |  |

| PD Input Voltage                                             | 37V to 57V                                                      | 42.5V to 57V                                                       |  |

| Guaranteed Current at PD Input                               | 350mA DC with up to<br>400mA peaks                              | 600mA DC with up to<br>686mA peaks                                 |  |

| Maximum Cable Resistance                                     | 20Ω                                                             | 12.5Ω                                                              |  |

| Physical Layer Classification                                | Mandatory<br>(no class = Class 0)                               | Mandatory                                                          |  |

| Supported Physical Layer Classification<br>Classes           | Class0 to Class3                                                | Class 4 - mandatory                                                |  |

| Data Link Classification                                     | Optional                                                        | Mandatory                                                          |  |

| 2-Events Classification                                      | Not required                                                    | Mandatory                                                          |  |

| 4 pairs power receiving                                      | Allowed                                                         | Allowed                                                            |  |

| Communication Supported                                      | 10/100 BASE-T<br>(Midspans)<br>10/100/1000 BASE-T<br>(switches) | 10/100/1000 BASE-T<br>Including Midspans (both<br>type1 and type2) |  |

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

COMPANY CONFIDENTIAL

# PD70101/PD70201 Features

- IEEE 802.3af (IEEE802.3at Type 1) Compliant (PD70101)

- IEEE802.3at Type 2 Compliant (PD70201)

- Support up to 47.7W 4 pair systems with a single PD70201

- Provides PD Detection Signature

- Programmable PD Classification Signature

- Supports 2 Event Classification Flag (PD70201)

- Active Low, Open Drain Power Good Signal

- Integrated Isolation Switch

- 24.9KΩ signature resistor disconnection when power is on

- Inrush Current Limit (Soft Start)

- Integrated 10.5V Start-up Supply for integrated DC/DC controller

- Internal Discharge Circuitry for up to 220µF DC/DC Bulk Capacitor

- Wide Temperature Operating Range -40°C to +85°C

- On-Chip Thermal Protection

- 100 kHz to 500 kHz adjustable DC-DC switching frequency

- DC/DC frequency can be synchronized to external clock

- Supports low power mode operation for higher efficiency

- Soft-start circuit to control the output voltage rise time

- Support efficient synchronous rectification

- PoE Port Input UVLO with programmable threshold and hysteresis

- Internal differential amplifier simplifying nonisolated step down converter

- Over load and short circuit protection

# Using PD70101/PD70201: Front End Section

The PD70101's Front End section provides the necessary Detection, Classification, and Isolation Switch control functions for a PoE-powered device conforming to IEEE 802.3af or 802.3at type 1 standards. The PD70201's Front End section provides the same functions as the PD70101, with an additional higher Isolation Switch current capability, additional 2-Events- Classification detection and AT Flag generation conforming to IEEE 802.3at type 2 standards. Both chips are designed for minimal external components.

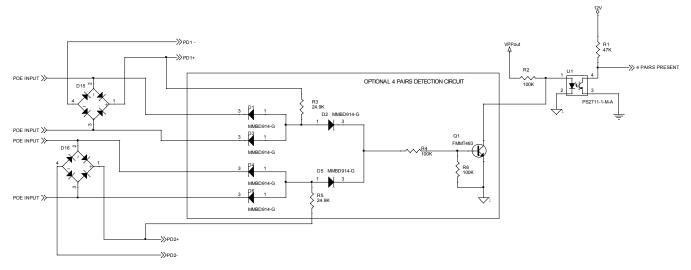

PD70101/PD70201 IC may be configured as an alternate two or four pair system (see Figure 2) in which one PD70101/PD70201 IC is driven from both diode bridges (output terminals connected in parallel), or may be configured as a four pair system (see Figure 3) in which a single PD70101/PD70201 IC and a single PD70100/PD70200 IC are driven individually by one of the two diode bridges. In four pair, two IC systems the isolation switch output terminals of the PD70101/PD70201 IC and the PD70100/PD70200 IC are connected together in parallel, and the two chips VPP inputs are isolated from one another by using two suitable diodes, each in series with VPP. For each IC, required capacitors of 50nF to 120nF (68nF typically used) are connected across the positive and negative output terminals of the each diode bridge. This configuration, as opposed to the two pair system, allows available output power to affectively double.

In an alternate two pair/four pair single IC system, the two input diode bridge's outputs are wired in parallel, and the common output supplies input power (VPP (+), VPN IN (-)) to the PD70101/PD70201 IC, which by means of the integrated PWM controller, drives an isolated or non-isolated DC/DC converter (depends on application requirements). The paralleled output terminals from the two diode bridges are connected to the PD70101/PD70201 IC at VPP (positive connection, pin 32), and VPN IN (negative connection, pin 5). This connection requires a single capacitor of 50nF to 120nF (68nF typically used) connected across the positive and negative output terminals of the paralleled diode bridges. This 68nF capacitor meets the IEEE 802.3af/at standard requirement for hardware detection.

The output connections from the PD70101/PD70201 Front End section are made at VPP (positive connection, pin 32), and VPN\_OUT (negative connection, pin 8). VPN\_OUT is the primary ground connection from the integrated isolation switch of the PD70101/PD70201 IC to the DC/DC converter. The IC's exposed center pad should be connected electrically to VPN\_IN (pin 5)

In addition to the PD70101/PD70201 Front End section's basic input/output connections, the following components are required for a typical application:

- Detection Resistor: Connect a 24.9kΩ ±1% resistor between VPP and RDET (Pin 1). This resistor is used to satisfy the Detection signature. A low wattage type may be used as there is less than a 7mW stress on this resistor while Detection phase is active, and the resistor is disconnected after power is on.

- Reference Resistor: Connect a 243kΩ ±1% resistor between RREF (pin 3) and VPN\_IN (pin 5). This resistor should be located as close as

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

practical to the PD70101/PD70201 IC. A low wattage type may be used (there is less than 1mW stress on this resistor).

**COMPANY CONFIDENTIAL**

- Classification Current Resistor: The value of this resistor determines the PD current draw during Classification Phase. Values corresponding to IEEE compliant classification levels are shown in Table 4. Connect this resistor between RCLASS (pin 4) and VPN\_IN (pin 5).

- Power Good Pull-up: Power Good signal is available at PGOOD (pin 2). A PGOOD flag is generated low voltage to optionally inform the application that the power rails for the integrated DC/DC controller are ready, and the DC/DC has begun soft-start. This signal can be used to disable any external input to the PD70101/PD70201's ENABLE pin (pin 10) when operating in a 4-pairs dual IC configuration. PGOOD is an open drain pin which requires a resistor pull-up to be functional. Pull-up voltage on this pin cannot exceed 74V and is recommended to be pulled up to a voltage no higher than VPP. This pin active low and rated at 0.4V and 0.75mA.

- AT Flag Pull-up (PD70201 only): AT Flag signal is available at AT\_FLAG (pin 7). An AT\_FLAG is generated low voltage to inform the application that the PSE providing PD power is IEEE 802.3at compliant. This is an open drain pin which

requires a resistor pull-up to be functional. Pull-up voltage on this pin cannot exceed 74V and is recommended to be pulled up to a voltage no higher than VPP. This pin is active low and rated at 0.4V and 0.75mA.

Start-up Supply Output Capacitor: The PD70101/PD70201 contains an internal low power (2mA continuous) regulated DC output available for use as a start-up supply for the integrated DC/DC converter controller. This supply output is available on the VCC pin (pin 31), and is intended to be used in conjunction with an external bootstrapped supply, also connected to the VCC pin. The PD70101/PD70201's VCC pin provides power input to the internal supply rails for the integrated DC/ DC controller. The bootstrapped supply input to VCC is typically provided by means of an auxiliary output from the DC/DC converter, but may be provided by means of any voltage source with a maximum output voltage of 15V (15V provides a safe operating range for the gate drive outputs). The internal start-up supply regulator requires a ceramic capacitor of minimum 4.7µF, to be connected directly between VCC (pin 31) and VPN OUT (pin 8).

| Programmed Classification Signature<br>RCLASS Resistance Values |           |                                                       |         |        |

|-----------------------------------------------------------------|-----------|-------------------------------------------------------|---------|--------|

| Class RCLASS Resistor                                           |           | PD70101/PD70201 Current<br>Draw During Classification |         |        |

|                                                                 | Value     | Min.                                                  | Average | Max.   |

| 0                                                               | Open      | 0                                                     |         | 3mA    |

| 1                                                               | 113Ω ±1%  | 9.5mA                                                 | 10.5mA  | 11.5mA |

| 2                                                               | 64.9Ω ±1% | 17.5mA                                                | 18.5mA  | 19.5mA |

| 3                                                               | 42.2Ω ±1% | 26.5mA                                                | 28mA    | 29.5mA |

| 4                                                               | 30.9Ω ±1% | 38mA                                                  | 40mA    | 42mA   |

#### Table 4: RCLASS Resistance Values

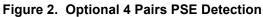

A single PD70101/PD70201 IC may be operated with 4 pairs for extended power capability. Up to 47.7W (PD70201 operating at IEEE 802.3at input voltage levels) is supported. The component requirements for a single PD70101/PD70201 operating with 4 pairs are the same as single IC applications operating with 2 pairs. A typical 2 pairs/4pairs single IC configuration is outlined in Figure 3.

Some applications may require an indication if power is provided on 4 pairs, or 2 pairs only. An additional circuit may be optionally added to sense if input POE power is provided on 2 pairs or 4 pairs. This circuit is shown in the application example of Figure 2.

Referencing the optional circuit of Figure 2, the PD70101/PD70201 detection resistor, RDET, is not used, and is replaced by two detection resistors, R3 and R5, which provide the required resistor detection signature for each individual 2 pairs input. R3 and R5 also provide pull up current so that the presence of the individual 2 pairs input may be sensed and combined into a logical OR function via diodes D1 thru D6. The output of this circuit is then used to

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

drive the switch circuit R4, R6, and Q1. The signal present at the Collector of Q1 will be low if only 2 pairs are present and high if all 4 pairs are providing power. Be aware that the output of this 4 pairs detection circuit is at POE voltage levels, and should not directly interface to low-level logic. If required, the Collector of Q1 can interface directly to an optoisolator as shown in the example.

WWW.IVICTOSettii

Page 6

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

#### Figure 3. Typical 2 or 4 Pair Configuration with a Single PD70201 IC.

In a 4 pairs dual IC system, a single PD70101/PD70201 IC and a single PD70100/PD70200 are placed in a PD design, each driven by a separate diode bridge. The Isolation Switch output at VPN\_OUT is connected in parallel for each IC, while the VPP inputs to PD70101 and PD70100 or PD70201 and PD70200 ICs are connected by means of series blocking diodes. The combined output terminals drive the input filter/bulk capacitor for the DC/DC converter. This affectively doubles the total input power capability to the DC/DC converter.

Under certain conditions, power available at the PI may be on two pairs only. Dual IC configurations where power is applied to only one of the two chips require certain considerations for the AT\_FLAG and PGOOD signals.

The AT\_FLAG should be connected in a wired-OR configuration. Since the AT\_FLAG output is open drain configured, this signal may be easily wired-OR between the PD70101/PD70201 and PD70100/PD70200 ICs for a common AT\_FLAG output connection by simply connecting the two AT\_FLAG pins together with a common pull-up resistor.

In a dual IC configuration, the PGOOD signal from the PD70100/PD70200 is used to enable the PD70101/PD70201's integrated DC/DC controller during conditions when the PD70101/PD70201's Front End section is not powered, and as such requires special consideration. The

PD70101/PD70201's ENABLE pin (pin 10) is active high; it should be tied to ground when it is not used. An example of a dual chip use of DC/DC enable control is shown in Figure 4.

Providing individual PGOOD and AT\_FLAG controls between two ICs is necessary for covering all possible power input configurations.

The  $V_{AUX}$  regulator output from the single PD70100/PD70200 IC must be connected to the VCC pin of the PD70101/PD70201 IC using a suitable blocking diode. In addition, a blocking diode must be added between the PD70101/PD70201 IC's VAUX pin (pin 31) and VCC pin (pin 30). Small, low current 30V diodes may be used for this requirement.

A typical 4 pairs, 2 IC configuration is outlined in Figure 4.

# Operation with an External (non POE) DC Source

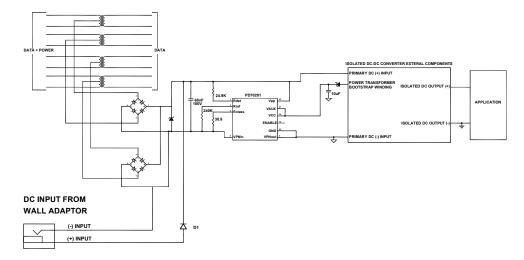

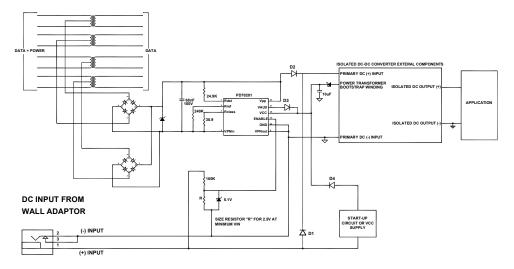

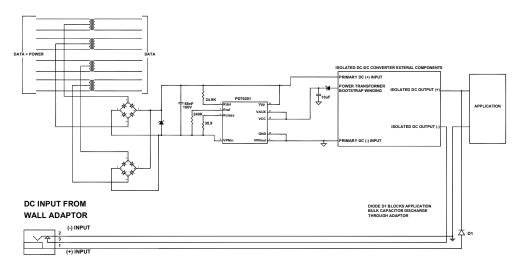

PD applications utilizing the PD70101/PD70201 IC may be operated with an external power source (DC wall adaptor). There are three methods of providing power with an external source:

External source connected directly to the PD70101/PD70201 Input (VPP to VPN\_IN). Requires external source output voltage to be 40V minimum under all load conditions. The adaptor must provide a diode in series with VPP to block reverse current from a fully charged bulk capacitor.

External source connected directly to the 2) PD70101/PD70201 output connection to the application. The external source output voltage will be dependent on the application input requirements. Both the external source and the PD70101/PD70201 IC's VPP must have series diodes to block reverse current. If the application's DC/DC converter contains a bootstrapped output connection to VCC, a suitable start-up circuit must be supplied for the external source, as the PD70101/PD70201's internal start-up supply will not function while powering the application with an external source in this configuration. In addition to the start-up supply requirement, an external enable signal is required, as the PD70101/PD70201's internal enable will not function while powering the application with an external

#### Designing a Type-1/2 IEEE 802.3at/af Powered Device

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

source in this configuration. If required, the additional start-up circuit and enable circuit will depend on the application requirements. Note: When not operating with an external adaptor, the PD70101/PD70201 IC's external enable pin should be tied to the GND pin (pin 23).

3) External source connected directly to the application's low voltage supply rails (output side of an isolated or non-isolated power supply). It is recommended the external source contain a series reverse current blocking diode and may optionally be isolated from the application power supply's output by means of a switched connection.

Three examples of PD70101/PD70201 configured with an external wall adaptor are diagrammed in Figure 5.

Figure 4: Typical 4 pairs configuration with a PD70200 and PD70201; shows use of ENABLE pin

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

#### **COMPANY CONFIDENTIAL**

#### CONFIGURATION #1: SOURCE CONNECTED TO PD70201 INPUT

#### CONFIGURATION #2: SOURCE CONNECTED TO PD70201 DC-DC CONVERTER

CONFIGURATION #3: SOURCE CONNECTED TO APPLICATION'S SUPPLY RAILS

Figure 5. External Power Input Configurations

#### Soft Start Current Limit

The PD70101/PD70201 IC provides Soft Start current limiting. A rising voltage of 36V to 42V between VPP and VPN\_IN will enable the isolation switch in Soft Start Current Limit mode. During this time, the current through the isolation switch is limited to 240mA (typical). The PD70101/PD70201 IC continuously monitors the voltage drop across the isolation switch (VPN\_OUT to VPN\_IN) during Soft Start mode. When difference between voltages VPN\_OUT and VPN\_IN drops below 0.7V, the PD70101/PD70201 IC will switch to normal operating mode, in which the isolation switch is fully on, with over-current protection circuitry active.

Soft Start current limit is necessary to limit the inrush current created by the initial charge up of input capacitors upon system start-up. Large inrush currents can create large voltage sags at the PI, which in turn can cause system functions tied to event thresholds (such as AT\_FLAG) to reset to their initial states. Soft Start current limit will significantly reduce the voltage sag upon start-up.

The PD70101/PD70201 IC Soft Start function limits current to a maximum of 320mA (240mA typical). Start-up into a fully discharged bulk capacitor will result in large power dissipation in the isolation switch for a period of time dependent on the size of the bulk capacitance. This occurs due to the initial voltage drop across the isolation switch. The maximum initial voltage drop across the isolation switch can be of 42V. In other words, the initial power dissipation of the isolation switch can be no higher than 13.4W (42V x 320mA). The maximum power dissipated by the isolation switch will decrease as the bulk capacitor charges, eventually decreasing to a maximum normal operating power dissipation of 74mW (PD70101) or 311mW (PD70201). The period of time required to switch from Soft Start mode to normal operation mode can be calculated using the following formula:

$$T = \frac{\left(\Delta V - 0.7\right) \times C}{I}$$

Whereas:

I = PD70101/PD70201 IC's current during soft start

C = Total input bulk capacitance

DV = Initial VPN\_OUT - VPN\_IN voltage at start of soft start (DVmax = VPP)

The PD70101/PD70201 IC can safely operate with a total bulk capacitance of  $220\mu F$ .

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

#### **Bulk Capacitor Discharge**

The PD70101/PD70201 IC provides discharge of the application bulk capacitor when VPP - VPN IN falling voltage drops below the isolation switch turn-off threshold (31V to 34V). This feature insures that the application bulk capacitance does not discharge through the detection resistor, which can cause the detection signature to fail and prevent the PSE from starting the PD. While enabled, the discharge function provides a minimum controlled discharge current of 23.8mA, which flows through the VPP pin, internally through the isolation MOSFET's body diode, and out through the VPN\_OUT pin. The discharge circuitry monitors the voltage difference between VPP - VPN OUT, and remains active while the difference voltage is  $1.5V \le (VPP - VPN_OUT) \le 32V$ . The maximum time to discharge can be calculated by:

$$T = \frac{\left(\Delta V - 1.5V\right) \times C}{0.0228}$$

Whereas:

C = Total Input Bulk Capacitance

DV = Initial VPP – VPN\_OUT Voltage at Isolation Switch Turn-off

Example: Assuming an initial capacitor voltage of 32V, it will take 294ms for a  $220\mu$ F capacitor to discharge to a 1.5V level.

The PD70101/PD70201 discharge circuitry can be safely operated with a bulk capacitance of up to  $220\mu$ F.

$V_{\text{AUX}}$  regulated output is enabled only when the isolation switch is in normal operation mode. This insures DC/DC controller does not start prematurely.

#### **PGOOD Output**

PD70101 and PD70201 IC provide an open drain output indicating POE power good status. This output is in a high impedance state until VPP – VPN\_IN voltage exceeds the isolation switch turn-on threshold, and isolation switch moves from Soft Start current limit mode to normal operation mode. Upon assertion, the PGOOD output switches to ground. When VPP – VPN\_IN voltage falls below the isolation switch turn-off threshold, the PGOOD output reasserts back to high impedance state.

#### COMPANY CONFIDENTIAL

#### AT\_FLAG Output (PD70201 only)

The PD70201 IC provides an open drain output indicating a 2 Events Classification was detected. This output is in a high impedance state until the VPP – VPN\_IN voltage exceeds the isolation switch turnon threshold and the isolation switch moves from Soft Start Current Limit mode to normal operation mode. It will then assert to low, but only if a 2 Events Classification Signature was recognized during Classification phase described earlier. Upon assertion, the AT\_FLAG output switches to ground. The AT\_FLAG output re-asserts back to the high impedance state when the VPP – VPN\_IN voltage falls below the isolation switch turn-off threshold.

The AT\_FLAG signal is synchronized with the PGOOD signal. For example, PGOOD can be asserted without asserting AT\_FLAG, but AT\_FLAG cannot be asserted without asserting PGOOD.

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

The AT\_FLAG signal is typically used for indicating the PD application that PSE is capable of supplying AT power levels. Often the PD application is electrically isolated. The AT\_FLAG is referenced to the primary ground. As such, it requires an optoisolator to provide an isolation barrier between primary ground and application ground for electrically isolated applications.

#### **Thermal Protection**

The PD70101/PD70201 IC provides thermal protection. Integrated thermal sensors monitor the internal temperatures of the isolation switch and classification current source. If the overtemperature threshold of either sensor is exceeded, that sensor's respective circuit will disable.

To insure trouble free operation, it is important that PD70101/PD70201 IC's exposed pad is mounted to a copper area on the PCB that provides an adequate heatsink.

## Using PD70101/PD70201: PWM Controller Section

The PD70101/PD70201's PWM Controller section provides all functions necessary to control both isolated and non-isolated DC/DC topologies, including isolated Flyback and Forward converter topologies, as well as non-isolated Buck and Boost topologies. The following considerations should be made when using the PD70101/PD70201 PWM controller:

Frequency Setting Resistor (RFREQ): The value of this resistor determines the switching frequency, as well as sets the pin current for both SS and RCLP pins. The value of RFREQ is based on the following equation:

> Freq =  $10 \times 10^{9}$ /R<sub>FREQ</sub> Resistor Range =  $100 k\Omega$  to  $20 k\Omega$

• Soft Start Charge Current: The DC/DC soft start time is determined by the value of the

#### **COMPANY CONFIDENTIAL**

capacitor connected to the SS pin, and the SS pin's charging current. The charging current is calculated:

The time required for soft start to complete is determined by the time required for the SS pin voltage to transition from 0 to 1.1V (min). This can be calculated with the following equation:

• Low Power Mode Clamp Threshold: The Low Power Mode Clamp Threshold is set by the resistor connected between RCLP pin (pin 17) and GND. The value is determined by the following equation:

$$V_{CLAMP} = 0.3 \text{ x} (R_{CLP}/R_{FREQ})$$

The clamp voltage determines the threshold below which the DC/DC converter enters low power skip mode (LPM). This threshold is typically set as a percentage of the peak inductor current at maximum output load and minimum input voltage.  $V_{CLAMP}$  voltage equates to a percentage of peak current by the following:

$I_{LPM} = [(0.9 \times V_{CLAMP})/1.2] \times I_{PK (MAX)};$

$I_{PK (MAX)}$  = maximum peak inductor current set by the current sense resistor (assumes V<sub>RCS</sub> = 0.12V at maximum peak current).

During start up, it starts with LPM mode until Vcomp voltage goes higher than 0.2V and/or  $V_{CLAMP} \le 1.11x(V_{COMP}-0.25V)$ , ( $V_{COMP} \ge 0.25V$ ). Connecting the RCLP pin to ground disables LPM mode during normal operation.

• VPP UVLO: The PD70101/PD70201 ICs offer a VPP monitoring UVLO function. The UVLO function is dependent on the voltage present at the VINS pin (pin 11), and will switch states based on a 1.2V threshold. Hysteresis may be programmed in by means of a resistor connected between HYST pin (pin 12) and VINS pin. Components are determined as follows:

$V_{HYST}$  = HYST Pin Output High (5V typ.)

V<sub>h</sub> = Desired Hysteresis

V<sub>RISING</sub> = Upper Voltage Threshold

Set R3 such that  $(V_{HYST} - 1.2)/R3 \le 10uA$

$$R1 = R3 \times (V_h/V_{HYST})$$

$$R2 = 1/[(V_{RISING}/(1.2 \times R1)) - (1/R1) - (1/R3)]$$

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

#### **Design Example**

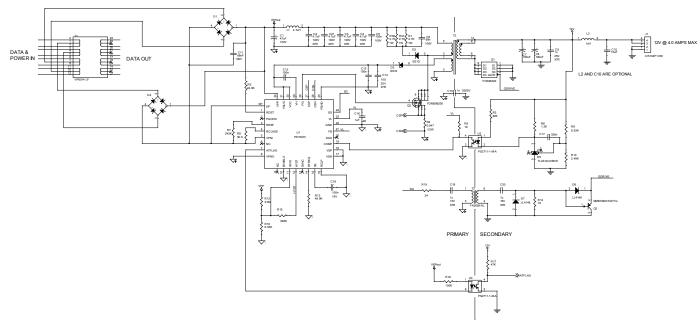

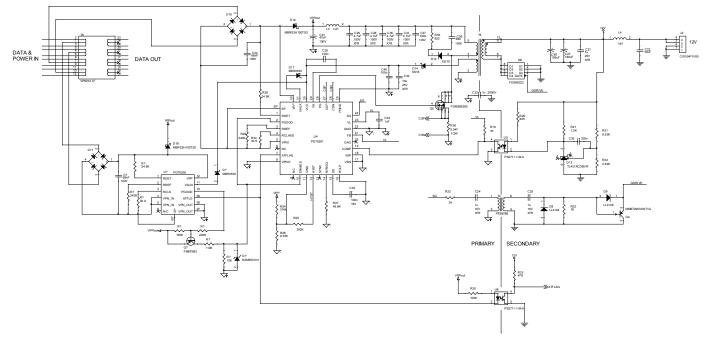

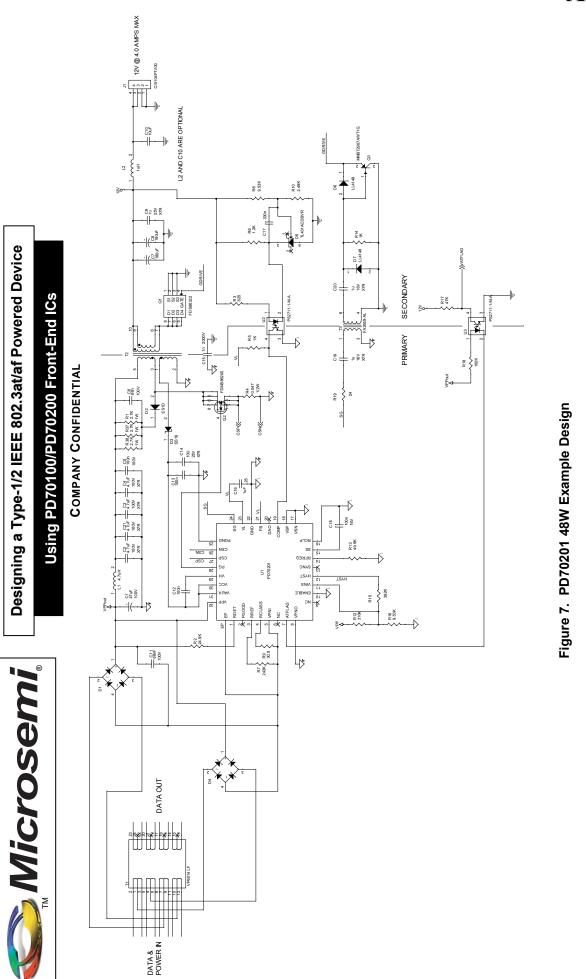

The following is a design example for a 48W DC/DC Flyback converter using the PD70201 IC. A schematic and parts list of the 48W example can be found in Figures 7.

• Design Requirements:

| <u>Vmin</u> := 32                               | Minimum Input Voltage                       |

|-------------------------------------------------|---------------------------------------------|

| <u>Vmax</u> := 57                               | Maximum Input Voltage                       |

| <u>Vout</u> := 12                               | Output Voltage                              |

| <u>Pout</u> := 48                               | Maximum Output Power                        |

|                                                 |                                             |

| <u>Eff</u> := .90                               | Estimated Efficiency                        |

| <u>Eff</u> := .90<br><u>Fsw</u> := 200 <u>k</u> | Estimated Efficiency<br>Switching Frequency |

|                                                 |                                             |

Flyback operation in DCM is best for output power less than 30W; therefore the design will be a CCM design.

#### • Estimated Secondary Diode Drop:

Synchronous Rectification is used in place of a blocking diode; choose FDMS86322 N-FET.

Sync Transistor: FDMS86322; RDSon = 0.008 at 25°C

| $\underline{lout} := \frac{\underline{Pout}}{\underline{Vout}}$ | <u>lout</u> = 4        |

|-----------------------------------------------------------------|------------------------|

| <u>Kt</u> := 1.58                                               | Multiplier for 100°C   |

| <u>rdson</u> := 0.008· <u>Kt</u>                                |                        |

| <u>ddrop</u> := <u>lout</u> ·rdson                              | <u>ddrop</u> = $0.051$ |

Transformer Turns Ratio:

Transformer Turns Ratio is driven by Vmin, Vout, the secondary diode drop, and the controller's maximum duty cycle. Per the datasheet, maximum duty cycle for the PD70201 = 46%.

<u>Dmax</u> := 0.46

$$\underline{\text{Tratio}} \coloneqq \frac{\underline{\text{Vout}} + \underline{\text{ddrop}}}{\underline{\text{Dmax}} \cdot \underline{\text{Vmin}}} - \frac{\underline{\text{Vout}} + \underline{\text{ddrop}}}{\underline{\text{Vmin}}}$$

Tratio = 0.442 Secondary to Primary (Ns/Np) Turns Ratio

For our design, we will increase the Turns Ratio to 0.444. 0.444 gives a Np/Ns Turns Ratio of 2.25:1, a more practical value.

#### Required Primary Inductance:

Minimum required primary inductance is based on

the desired ripple factor (Krf), which is defined as

inductance changes from CCM to DCM operation.

between 0.5 to 1.4. For our design, we will set it

<u>Krf</u> := 0.7 Krf is the ratio of inductor ripple to inductor average current

+ ddrop

Tratio

<u>Lnom</u> =  $3.512 \times 10^{-5}$

**Transformer Primary/Secondary Currents:**

+ Ipriavg

$\frac{|\text{pripk}^2 - (\text{pripk} \cdot \text{priripple}) + \frac{|\text{priripple}^2|}{2}}{2}$

lsecpk = 11.016

Isecpk ·

lsecpk<sup>2</sup>

Dmax)

Ipriripple

Tratio

Vout + ddrop

Tratio

linavg = 1.667

Ipriavg = 3.623

<u>lpriripple</u> = 2.536

lpripk = 4.891

+ <u>Eff</u>·<u>Vmin</u>

the percentage of peak to peak inductor ripple

current versus inductor average current. This

number sets the point in which the primary

A good rule of thumb is to set this number

to 0.7.

Lpri :

Krf · Fsw · Pout · Vmin

Nominal Primary Inductance (allows for +/- 15%):

<u>Lpri</u> =  $3.054 \times 10^{-5}$

$\underline{\text{Lnom}} := \underline{\text{Lpri}} \cdot 1.15$

linavg:=

Ipriavg:=

Ipripk :=

Iprirms :=

Isecpk :=

Isecrms :

lprirms = 2.507

Primary Ripple:

Average Input Current:

Pout

Eff · Vmin

Average Primary Current: linavg

Dmax

Ipriripple := Ipriavg Krf

Peak Primary Current: Ipriripple

Primary Circuit RMS Current:

Dmax.

Secondary Circuit RMS Current:

Ipripk

Tratio

#### Designing a Type-1/2 IEEE 802.3at/af Powered Device

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

#### **Transformer Specifications:**

Based on the calculations above, the following can be given to a transformer manufacturer for transformer fabrication:

Primary Voltage Range:

Vmin = 32

<u>Vmax</u> = 57

Secondary Voltage & Power:

$$Vout = 12$$

$Pout = 48$

Auxilliary Voltage & Power:

Paux = 1.2 <u>Vaux</u> = 12

Switching Frequency  $\underline{\mathsf{Fsw}} = 2 \times 10^5$

$$\underline{Dmin} := \frac{\underline{Vout} + \underline{ddrop}}{\underline{Vout} + \underline{ddrop} + \underline{Tratio} \cdot \underline{Vmax}} \qquad \underline{Dmin} = 0.323$$

Maximum Primary Operating Volt-Seconds:

$$\underline{\text{Vsecmax}} := \frac{\underline{\text{Dmin}} \cdot \underline{\text{Vmax}}}{F_{\text{SW}}} \qquad \underline{\text{Vsecmax}} = 9.193 \times 10^{-5}$$

Open Circuit Primary Inductance (+/- 15%):

$$Lnom = 3.512 \times 10^{-5}$$

Turns Ratio:

Naux :=

$$\frac{Vaux}{Vout}$$

Turns Ratio Calculation for Aux WindingNsec/Npri: $\underline{Tratio} = 0.444$ Npri/Nsec: $\frac{1}{\underline{Tratio}} = 2.252$ Naux/Nsec: $\underline{Naux} = 1$ Winding Currents:

| <u>lprirms</u> = 2.507 | <u>lpriavg</u> = 3.623 |

|------------------------|------------------------|

| <u>lpripk</u> = 4.891  | <u>lsecrms</u> = 6.118 |

#### **Primary Clamp Equations:**

The maximum transformer primary voltage seen across the V<sub>DS</sub> of the primary transistor during the off period will be greater than the maximum input voltage by a factor of the secondary voltage reflected by the transformer's turns ratio plus the voltage generated by the leakage inductance of the primary. Because of this, a suitable clamp is required to insure the primary voltage does not exceed the transistor's maximum V<sub>DS</sub>. There are many types of clamps available to the designer; each has it's merits and drawbacks. For this design the more common RCD clamp will be used. An example of an RCD clamp is outlined in

lsecrms = 6.118

Ipriripple<sup>4</sup>

Tratio

Page 13

www.Microsemi.com

#### COMPANY CONFIDENTIAL

figure 7. The first step is to select a maximum  $V_{\text{DS}}$  transistor rating. The reflected voltage is found:

Reflected Mosfet Drain Voltage:

$$\underline{Vd} := \left(\frac{\underline{Vout} + \underline{ddrop}}{\underline{Tratio}}\right) + \underline{Vmax} \qquad \underline{Vd} = 84.141$$

Vd=the reflected voltage across the transistor

Based on the above equation, the transistor selection will need to have a  $V_{DS}$  rating considerably larger than 85V. 100V does not leave margin for voltage overshoot, and would require significant power loss to achieve, so a 150V transistor will be used.

Next, the maximum clamp voltage and a clamping coefficient is calculated using the chosen  $V_{DS}$  rating de-rated by 15%. The clamping coefficient is simply the ratio

Clamp Voltage Limit (with BVdss derated):

$\underline{\text{Vclamp}} := \underline{\text{BVdss}} \cdot 0.85 - \underline{\text{Vd}}$

<u>Vclamp</u> = 43.359

Clamp Coeffient based on selected Turns Ratio:

$\frac{\text{Kccalc}}{(\text{Vout} + \text{ddrop})} = \frac{\text{Kccalc}}{(\text{Kccalc} + 1.598)}$

Maximum Transistor Stress Voltage:

<u>Vstress</u> := <u>Vd</u> + <u>Vclamp</u> <u>Vstress</u> = 127.5

$\underline{\mathsf{BVdss}} \cdot 0.85 = 127.5$

Using Leakage inductance estimated at 1% of the primary inductance, and the values calculated above, the final RC values are calculated:

Estimated Leakage Inductance:

Lleak := Lnom 0.01 Leakage is set at 1% of total primary inductance

Clamp Voltage Limit:

<u>Vclamp</u> = 43.359

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

Desired Clamp Capacitor Ripple Voltage:

$$\underline{\text{Vcripple}} := \underline{\text{Vclamp}} \cdot 0.1$$

Clamp Coefficient:

Resistor Calculation:

$$\underline{\text{Rclmp}} := \frac{(\text{Kccalc} - 1) \cdot \left[2 \cdot \text{Kccalc} \cdot (\text{Vout} + \text{ddrop})^2\right]}{\text{Tratio}^2 \cdot \text{Fsw} \cdot \text{Lleak} \cdot \text{lpripk}^2}$$

<u>Rclmp</u> = 837.011

Resistor Power Dissipation:

$$\underline{\text{PrcImp}} := 0.5 \cdot \underline{\text{Fsw}} \cdot \underline{\text{Lleak}} \cdot \underline{\text{Ipripk}}^2 \cdot \frac{\underline{\text{Kccalc}}}{\underline{\text{Kccalc}} - 1}$$

<u>PrcImp</u> = 2.246

Capacitor Calculation:

$\underline{Cclmp} := \frac{\underline{Kccalc} \cdot (\underline{Vout} + \underline{ddrop})}{\underline{Tratio} \cdot \underline{Rclmp} \cdot \underline{Fsw} \cdot \underline{Vcripple}}$

<u>Cclmp</u> =  $5.974 \times 10^{-8}$

Clamp Current Calculation:

Leak L Reset Time: <u>Trst</u> =  $1.059 \times 10^{-7}$

$$\underline{\text{lclmprms}} := \underline{\text{lpripk}} \cdot \sqrt{\frac{\underline{\text{Trst}} \cdot \underline{\text{Fsw}}}{3}}$$

lclmprms = 0.411

Based on the above equations, the clamp resistor will need to be 3 X 2.7K Ohm, 1W 5% resistors in parallel. The capacitor will need to be a  $.068\mu$ F, 100V capacitor.

Using the clamp current and maximum stress voltage the diode is selected. A fast diode is desired.

<u>Vstress</u> = 127.5

<u>IcImprms</u> = 0.411

A 200V, 1A ES1D Diode is selected.

Note that the above component selections will require final tweaking at the prototype stage.

**Primary FET Requirements:**

RDSon.

lprirms = 2.507

Chosen <sub>0ja:</sub>

Chosen Ambient T:

Transistor BVdss:

Transistor Qgs2:

Transistor Qgd:

Plimit

Chosen Max. Junction T:

Transistor Power Limit:

Tamb

θia

Transistor gate resistance:

Gate drive on resistance:

Gate drive off resistance:

Transistor gate threshold voltage:

Transistor gate drive max voltage:

**COMPANY CONFIDENTIAL**

The primary FET will be chosen based on maximum primary RMS current, and maximum  $V_{DS}$  stress. Note that the maximum stress has already been accounted for; we will chose a 150V

FET based on the primary RMS Current and

A FDMS86200 FET by Fairchild has a V<sub>DS</sub> rating of 150V, maximum continuous  $I_{DS}$  rating of 9.6A, and a specified RDSon of  $18m\Omega$  at 25°C.

RDSon := .03

$\theta \mathbf{j} \mathbf{a} := 50$

<u>Ti</u> := 100

<u>Tamb</u> = 70

BVdss = 150

$\underline{\text{Plimit}} = 0.6$

Qgs := 2.9n

Qgd := 7.7n

Rg := 1.2

Vgsmiller := 3.9

Vth := 2.5

<u>Vcc</u> := 12

$\frac{\text{Rhi}}{\text{Rlo}} := 10$

**Primary FET Power Dissipation:**

Selected Transistor: FDMS86200 Chosen RDSon (at 100°C):

#### Designing a Type-1/2 IEEE 802.3at/af Powered Device

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

Falling Gate Current and Turn-off Time:

| $\underline{lgf1} := \frac{Vcc - [0.5 \cdot (Vgsmiller + Vth))}{Rlo + Rg}$                                                                                                                                      | <u>lgf1</u> = 1.41935                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| $\frac{\text{lgf2}:=\frac{\text{Vcc}-\text{Vgsmiller}}{\text{Rlo}+\text{Rg}}$                                                                                                                                   | <u>lgf2</u> = 1.30645                                                                                     |

| $\Delta \underline{\text{toff}} := \frac{\underline{\text{Qgs}}}{\underline{\text{lgf1}}} + \frac{\underline{\text{Qgd}}}{\underline{\text{lgf2}}}$                                                             | $\Delta \underline{\text{toff}} = 7.93701 \times 10^{-9}$                                                 |

| Valley Current:                                                                                                                                                                                                 |                                                                                                           |

| <u>Ivalley</u> := <u>Ipriavg</u> $-\frac{1priripple}{2}$                                                                                                                                                        | <u>lvalley</u> = 2.30496                                                                                  |

| Operational Primary RMS Current:                                                                                                                                                                                |                                                                                                           |

| <u>lprirms</u> = 2.48022                                                                                                                                                                                        |                                                                                                           |

| Conduction Loss:                                                                                                                                                                                                |                                                                                                           |

| <u>Pcond</u> := <u>lprirms</u> <sup>2</sup> · <u>RDSon</u> <u>F</u>                                                                                                                                             | <u>Pcond</u> = 0.18454                                                                                    |

| Turn On Switch Loss:                                                                                                                                                                                            |                                                                                                           |

| $\underline{Pswon} := \frac{\underline{Ivalley} \cdot \left( \underline{Vmin} + \frac{\underline{Vout} + \underline{dd}}{\underline{Tratio}} \right)}{6}$                                                       | <u>rop</u> )∆ <u>ton</u><br>. <u>Fsw</u>                                                                  |

| <u>Pswon</u> = 0.06515                                                                                                                                                                                          |                                                                                                           |

| Turn Off Switch Loss:                                                                                                                                                                                           | <u>Vclamp</u> = 43.3591                                                                                   |

| $\underline{Pswoff} := \frac{\underline{lpripk} \cdot (\underline{Vmin} + \underline{Vclamp}) \cdot \Delta \underline{tr}}{2}$                                                                                  | $\frac{\text{off}}{\text{Fsw}} \cdot \frac{\text{Pswoff}}{\text{Pswoff}} = 0.28634$                       |

| Total Power Loss:                                                                                                                                                                                               |                                                                                                           |

| <u>Plosstot</u> := <u>Pcond</u> + <u>Pswon</u> + <u>Pswoff</u>                                                                                                                                                  | $\underline{Plosstot} = 0.53603$                                                                          |

| In the above calculations, R <sub>DS</sub><br>100°C. Values for Vth, Qgd a<br>in most MOSFET datasheets.<br>switching gate charge; if not s<br>estimated using the Vgs vs G<br>(found in all MOSFET datasheets) | and Rg are available<br>. Qgs2 is the<br>specified, it may be<br>ate charge graph<br>eets) by determining |

Rising Gate Current and Turn-on Time:

Transistor gate voltage at start of miller effect:

| $\underline{lg1} := \frac{\underline{Vcc} - [0.5 \cdot (\underline{Vgsmiller} + \underline{Vth})]}{\underline{Rhi} + \underline{Rg}}$ | <u>lg1</u> = 0.78571                              |

|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| $\underline{Ig2} := \frac{\underline{Vcc} - \underline{Vgsmiller}}{\underline{Rhi} + \underline{Rg}}$                                 | <u>lg2</u> = 0.72321                              |

| $\Delta \underline{ton} := \frac{\underline{Qgs}}{\underline{lg1}} + \frac{\underline{Qgd}}{\underline{lg2}}$                         | $\Delta \underline{ton} = 1.43378 \times 10^{-8}$ |

#### • Synchronous FET Requirements:

The output synchronous FET is chosen by calculating the maximum DS voltage created during the primary on time (sync FET is off), and the maximum secondary RMS current. To derate the FET, DS voltage is increased by 30% and DS current is increased by 50% for proper FET selection.

the equivalent charge between Vth and Vgsmiller.

Maximum Primary Reflected Voltage across FET:

Vsecref :=  $Vmax \cdot Tratio + Vout$ Vsecref = 37.308Vsecref  $\cdot 1.3 = 48.5$

Maximum FET Current (de-rated):

$\underline{\text{Irect}} := \underline{\text{Isecrms}} \cdot 1.5 \qquad \underline{\text{Irect}} = 9.177$

A FET is chosen with a  $V_{DS}$  of 60V or higher, and a current capability of 9 Amps or greater. Chosen is the FDMS86322. This FET has an  $R_{DS}$  on (25°C) of 0.007 at 13A, and a maximum  $V_{DS}$  of 80V.

#### • Synchronous FET Power Dissipation:

ddropcalc := Isecrms · rdson

$\underline{\text{ddropcalc}} = 0.077 \qquad \qquad \text{Voltage drop across the transistor}$

rdson = 0.013 Rdson at 100°C

Rectifier Power Loss:

$\underline{\text{Prect}} := \underline{\text{Isecrms}} \cdot \underline{\text{ddropcalc}} \qquad \underline{\text{Prect}} = 0.473$

Rectifier Junction Temp:

<u>Tamb</u> = 70

<u>Thetajarect</u> := 50 Package theta ja

<u>Jtrect</u> := <u>Thetajarect</u>  $\cdot$  <u>Prect</u> + <u>Tamb</u> <u>Jtrect</u> = 93.654

#### • Sense Resistor Calculation:

The sense resistor is chosen based on the maximum peak current expected, and the voltage threshold where the controller starts to limit current. For the PD70201, the current limit threshold voltage is 1.2V with a gain of 5 current sense amplifier, so the resistor is sized such that the operating peak primary current develops at approximately 90% of this value. 1.1V is approximately 90% of 1.2V.

$\underline{\text{Vthreshold}} := 1.1$

Sense Resistor Value (accounts for X5 gain):

| $\frac{\text{Rsns}}{\text{lpripk}} := \frac{\text{Vthreshold}}{\text{lpripk}} \cdot 5$ | <u>Rsns</u> = 0.04596 |

|----------------------------------------------------------------------------------------|-----------------------|

| Prsns := Iprirms <sup>2</sup> · Rsns                                                   | <u>Prsns</u> = 0.2827 |

The above takes into account Av = 5 for the current sense amplifier.

A  $47m\Omega$  1/2W resistor will meet the requirment.

#### Output Capacitor Calculation:

### Designing a Type-1/2 IEEE 802.3at/af Powered Device

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

| The output filter capacitor is chosen based on the desired output voltage ripple, output voltage undershoot (droop) during load step, and the RMS ripple current the capacitor must endure. |                                      |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|

| Desired Output Ripple: Vripple :=                                                                                                                                                           | 0.1                                  |  |

| Desired Closed-Loop Bandwidth:                                                                                                                                                              | <u>Fc</u> := 4 <u>k</u>              |  |

| Desired Output Droop Load Step:                                                                                                                                                             | <u>Vdroop</u> := 0.6                 |  |

| Load Step: <u>Istep</u> := <u>lout</u> 0.9                                                                                                                                                  |                                      |  |

| <u>lsecpk</u> = 11.016                                                                                                                                                                      |                                      |  |

| <u>loutavg</u> := <u>Iinavg</u><br><u>Tratio</u>                                                                                                                                            | <u>loutavg</u> = 3.754               |  |

| <u>lsecrms</u> = 6.118                                                                                                                                                                      |                                      |  |

| <u>Icoutrms</u> := $\sqrt{1 \text{secrms}^2 - 1 \text{outavg}^2}$                                                                                                                           | <u>lcoutrms</u> = 4.831              |  |

| <u>Cesr</u> := <u>Vripple</u><br><u>Isecpk</u>                                                                                                                                              | <u>Cesr</u> = $9.077 \times 10^{-3}$ |  |

| $\underline{Cout} := \frac{\underline{Istep}}{2 \cdot \pi \cdot \underline{Vdroop} \cdot \underline{Fc}}$                                                                                   | <u>Cout</u> = $2.387 \times 10^{-4}$ |  |

| <b>. .</b>                                                                                                                                                                                  |                                      |  |

Chosen Output Capacitor:

$\underline{Coutact} := 360\underline{u}$

<u>Cesract</u> := 0.008

For the output capacitor, we will choose 2x Sanyo OSCON 25SVPF180M capacitors in parallel. These are  $180\mu$ F, 25V capacitors with an ESR of 16m Ohm and a maximum ripple capability of  $4.65A_{\text{RMS}}$ .

#### Input Filter Calculation:

The input filter is used to reduce the voltage fluctuations seen at the DC/DC converter input due to the large peak currents involved. There are several approaches to providing an input filter; the input filter can consist of a simple input capacitor (usually several capacitors in parallel due to the large ripple currents), or can be a more complex LC filter. For this design, we will choose an LC filter as our input filter. The input to the LC filter will be a common aluminum electrolytic; the output of the LC filter will consist of smaller ceramic capacitors to absorb the ripple current.

AN-194

www.Microsemi.com

#### COMPANY CONFIDENTIAL

Our design requires the ripple voltage on VPP to be 50mV or less. We will first choose a suitable ripple voltage at the primary, and then size the input capacitor to achieve that ripple voltage. The input capacitor will need to absorb most of the primary ripple current, so it's ripple handling capability is critical. Ceramic capacitors have very good ripple current capability and are a good choice for the input capacitor for this design.

First we will determine the maximum ripple current seen by the capacitor, and use this use this current to select a suitable input capacitor based on our selected primary ripple of 320mV:

Cinputrms :=

$$\sqrt{\frac{1 \text{ prirms}^2 - \frac{1 \text{ linhigh}^2}{2}}$$

Cinputrms = 1.873

<u>Vinripple</u> := 0.32

<u>Cmin</u> := <u>Cinputrms</u>·Dmax <u>Fsw</u>·Vinripple

```

<u>Cmin</u> = 1.34888 \times 10^{-5}

```

For this design, we will choose  $4x 4.7\mu$ F 100V ceramic capacitors in parallel. 4 capacitors are chosen to account for capacitor tolerance variation. The ceramic capacitors chosen (1812 case size) have a ripple capability at 100 kHz of greater than 2A for a 20°C case temperature rise.

The capacitors chosen will meet more than this requirement.

Next, we will determine the voltage developed across our chosen input capacitors:

<u>Cminact</u> := 15<u>u</u> Actual capacitance - 20% tolerance

<u>Cinesr</u> := 1.2<u>m</u>

$\underline{\text{deltavin}} := \frac{\underline{\text{Cinputrms}} \cdot \underline{\text{Dmax}}}{\underline{\text{Fsw}} \cdot \underline{\text{Cminact}}} + \underline{\text{Ipriavg}} \underline{\text{Cinesr}}$

<u>deltavin</u> = 0.29202

Next we will chose an inductor based on the desired attenuation. For this design, we will attenuate the input current by 40dB:

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

Filter Attenuation Desired:

Filter Cutoff Frequency for Required Attenuation:

$$\underline{\mathsf{Fo}} \coloneqq \sqrt{\underline{\mathsf{A}}} \cdot \underline{\mathsf{Fsw}} \qquad \underline{\mathsf{Fo}} = 2 \times 10^4$$

Required Lin vs Cin:

$$\underline{\text{Lin1}} := \frac{1}{4\pi^2 \cdot \underline{\text{Fo}}^2 \cdot \underline{\text{Cminact}}}$$

$\underline{\text{Lin1}} = 4.22172 \times 10^{-6}$

$\underline{InputfilterIrms} := \underline{A} \cdot \underline{Cinputrms}$

InputfilterIrms = 0.01837

For this design we will use a  $4.7\mu$ H inductor. This inductor needs to handle the maximum Primary RMS current at low line, and should be sized with a minimum DCR to increase efficiency.

Finally, we will need to check our filter for stability. In order for the filter to be stable, the filter output impedance must be less than the input impedance of the DC-DC converter. The input impedance is calculated at DC for a first order check. The filter output impedance is compared at two frequency points: DC (which is simply the DCR of the inductor), and at the resonant point where peaking occurs due to the filter Q:

| $\frac{Zinsmpsdc}{Zinsmpsdc} := \frac{Vmin^2 \cdot \underline{E}}{\underline{Pout}}$ $\frac{Zinsmpsdc}{\underline{Zinsmpsdc}} = 19.2$ | Converter Input Impedance at DC |

|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| $\underline{\text{Zoutfilterdc}} := \underline{\text{DCR}}$ $\underline{\text{Zoutfilterdc}} = 0.045$                                 | Filter Output Impedance at DC   |

Filter Output Impedance at resonant point:

$$\underline{Zoutfiltermax} := \sqrt{\frac{(\underline{Cinact} \cdot \underline{ESR}^2 + \underline{Linact}) \cdot (\underline{Cinact} \cdot \underline{DCR}^2 + \underline{Linact})}{\underline{Cinact}^2 \cdot (\underline{ESR} + \underline{DCR})^2}}$$

#### Zoutfiltermax = 6.804

The calculated output impedance of our filter at DC is  $45m\Omega$ ; at the resonant point it is  $6.8\Omega$ . Both of these values are less than the Converter DC input impedance of  $19.2\Omega$ ; our filter values will not cause stability issues.

#### • Control Loop Calculations:

Control loop calculations are made by determining the modulator and filter gain and phase at the desired crossover frequency, and then selecting feedback components to increase

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

$\underline{\mathsf{Gxo}} := 20 \cdot \underline{\mathsf{log}} \left( \left| \underline{\mathsf{H}} (2 \cdot \pi \cdot \mathbf{i} \cdot \underline{\mathsf{Fc}}) \right| \right)$

$\underline{Gxo} = -5.179$  Gain at crossover point (dB)

$\underline{\mathsf{Pxo}} := \underline{\operatorname{arg}}(\underline{\mathsf{H}}(2 \cdot \pi \cdot \mathbf{i} \cdot \underline{\mathsf{Fc}})) \cdot \frac{180}{\pi}$

Pxo = -88.008 Phase shift at crossover point (Degrees)

Once the gain and phase are known, the loop must be closed such that the gain at the crossover frequency is equal to 1 (0dB), and the phase margin is greater than 45°.

In most isolated designs, the feedback loop is closed by means of an optocoupler which bridges the primary/secondary isolation barrier. The optocoupler is chosen to account for the isolation requirements and the input/output current gain (noted as a percentage, "CTR", which translates to the percentage of input LED current transferred to the output). For our design, the optocoupler will drive the PD70201's COMP pin directly. The optocoupler components are selected as follows:

Optocoupler Calculations:

| <u>Vf</u> := 1                                                                              | Optocoupler: NEC PS2                                                                        | 2711-1-M-A                                                    |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| <u>Vdd</u> := 5.0                                                                           | Vdd = PD70201's VL t                                                                        | ypical output voltage                                         |

| <u>Rpullup</u> := 1 <u>k</u><br><u>Vcesat</u> := 0.3                                        | Rpullup added to increase frequency                                                         | e Optocoupler pole                                            |

| Di 100 dat                                                                                  | ese values are fall time tes<br>asheet; used for estimating<br>= fall time, RI = test load. |                                                               |

| <u>CTRmax</u> := 2.00                                                                       |                                                                                             |                                                               |

| <u>CTRmin</u> := 1.00                                                                       |                                                                                             |                                                               |

| <u>loptomin</u> := <u>Vdd</u><br><u>Rpu</u>                                                 | <u>– 1.2</u><br><u>illup</u>                                                                | <u>loptomin</u> = $3.8 \times 10^{-3}$                        |

| $\underline{loptomax} := \left( \frac{Vd}{M} \right)$                                       | <u>d - Vcesat</u> ) + 500 <u>u</u><br><u>Rpullup</u> ) + 500 <u>u</u>                       | $\underline{loptomax} = 5.2 \times 10^{-3}$                   |

|                                                                                             | s 1.2 max regulation input<br>aximum Error Amp Comp                                         |                                                               |

| Optoisolator Cha                                                                            | racteristic Pole Capacitor:                                                                 |                                                               |

| $\underline{\text{Cpole}} := \frac{\underline{\text{Tf}}}{2.2 \cdot \underline{\text{RI}}}$ |                                                                                             | <u>Cpole</u> = $2.273 \times 10^{-8}$                         |

| ∞ <u>popto</u> :=<br><u>Rpullu</u>                                                          | <u>1</u><br><u>p·Cpole</u> <u>fpopto</u> := -                                               | $\frac{\omega \text{popto}}{2 \cdot \pi} = 7.003 \times 10^3$ |

| <u>Iledmin</u> :=<br><u>CTRm</u>                                                            | <u>nin</u><br>Iax Iledmin =                                                                 | $1.9 \times 10^{-3}$                                          |

COMPANY CONFIDENTIAL

(or decrease) the gain for unity gain at the crossover point. First, the modulator and filter must be evaluated to determine the frequency location of the Right Hand Plane Zero (inherent in CCM Flyback designs), and assure that the chosen crossover frequency is less than 20% of that frequency:

Calculation of Right Hand Plane Zero:

$\frac{\text{Rload}}{\text{Ezrhp}} := \frac{\frac{\text{Vout}}{\text{lout}}}{2\pi \text{ Dmax} \cdot \text{Lnom} \cdot \text{Tratio}^2} \qquad \qquad \text{Ezrhp} = 4.372 \times 10^4$

$\underline{\mathsf{Fzrhp}} \cdot 0.2 = 8.744 \times 10^3$

This number must be greater than the proposed crossover frequency.

Our proposed crossover frequency is 4kHz; we have plenty of margin.

The modulator and filter gain-phase of our regulator utilizes the following transfer function:

| $\underline{\text{Kcc}} := \frac{\underline{\text{Ipripk}}}{1.2}$ Current Control Factor                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\omega \underline{z1} := \frac{1}{\underline{\text{Cesract}} \cdot \underline{\text{Coutact}}} \qquad \text{Capacitor ESR zero}$                                                                                                                                                                                                                                             |

| $\omega \underline{z2} := \frac{(1 - \underline{Dmax})^2 \cdot \underline{Rload}}{\underline{Dmax} \cdot \underline{Lnom} \cdot \underline{Tratio}^2} \qquad \text{RHP zero}$                                                                                                                                                                                                 |

| $\omega \underline{p} := \frac{(1 + \underline{Dmax})}{\underline{Rload} \cdot \underline{Coutact}}$ Load pole                                                                                                                                                                                                                                                                |

| $\underline{\text{Vro}} := \frac{\underline{\text{Dmax}}}{1 - \underline{\text{Dmax}}} \cdot \underline{\text{Vmin}} \qquad \text{Reflected output voltage}$                                                                                                                                                                                                                  |

| $\underbrace{H}_{WV}(\underline{\mathbf{s}}) := \frac{Kcc \cdot Rload \cdot Vmin \cdot Tratio^{-1}}{2 \cdot Vro + Vmin} \cdot \frac{\left(1 + \frac{\underline{\mathbf{s}}}{\omega \underline{\mathbf{z}} 1}\right) \cdot \left(1 - \frac{\underline{\mathbf{s}}}{\omega \underline{\mathbf{z}} 2}\right)}{1 + \frac{\underline{\mathbf{s}}}{\omega \underline{\mathbf{p}}}}$ |

| Solving for H at the crossover frequency:                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                               |

# Microsemi<sub>®</sub>

#### COMPANY CONFIDENTIAL

On the secondary side, the optocoupler must be driven with an error amplifier that regulates the output voltage. Most designs utilize a common TL431 shunt regulator, due to it's ability to regulate without requiring additional input power for operation. The compensation components, as well as the DC setting resistors will be placed around the TL431. First, the DC setting resistors are calculated:

TL431 Calculations:

Reference Resistors:

<u>Vref</u> := 2.5

<u>Iref</u> := 4<u>u</u>

Iresistordivider:= 1m

Rlowercalc := <u>Vref</u>

<u>Iresistordivider</u> <u>Rlower</u> := 2.49<u>k</u>

Actual resistor used

<u>Rlowercalc</u> =  $2.5 \times 10^3$

Ruppercalc :=  $\frac{(Vout - Vref)}{Iresistordivider + Iref}$ Ruppercalc =  $9.462 \times 10^3$ Rupper := 9.53kActual resistor usedVoutcalc :=  $\left(\frac{Vref}{Rlower} + Iref\right) \cdot Rupper + Vref$ Voutcalc = 12.106

Next, the compensation components are selected:

#### 431 Compensation (Type Two):

| <u>Gxo</u> = $-5.179$ Modulator and Filter gain at Fc (dB)                                      |

|-------------------------------------------------------------------------------------------------|

| $\underline{\mathbf{Gc}} \coloneqq 10^{\left(\frac{\mathbf{Gxo}}{20}\right)}$                   |

| $\underline{Gc} = 0.551$ Modulator and Filter gain at FC (mag)                                  |

| <u>G431</u> := $\frac{1}{\underline{Gc}}$ = 1.815 Required feedback gain                        |

| $\underline{fz431} := 54$ Compensation Zero; set to 1/4 Load Pole                               |

| $\underline{\text{fp431}} := 14\underline{k}$ Compensation Pole; set to 1/4 ESR zero            |

| <u>Ibias</u> := 2 <u>m</u> 431 bias for regulation                                              |

| CTRtyp := 1.5 Optoisolator CTR typical                                                          |

| $\frac{\text{Rledcalc}}{\text{G431}} := \frac{\text{CTRtyp} \cdot \text{Rpullup}}{\text{G431}}$ |

| <u>Rledcalc</u> = 826.267 LED Resistor                                                          |

| 1                                                                                               |

<u>Czcalc</u> =  $3.093 \times 10^{-7}$  Calculated Zero Capacitor

2·π·Rupper·fz431

Czcalc :=

#### Designing a Type-1/2 IEEE 802.3at/af Powered Device

#### Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

<u>Cpcalc</u> :=  $\frac{1}{2 \cdot \pi \cdot \text{Rpullup} \cdot \text{fp431}}$

<u>Cpcalc</u> =  $1.137 \times 10^{-8}$  Calculated Pole Capacitor

<u>Cpole</u> =  $2.273 \times 10^{-8}$  Optoisolator Pole Capacitor

Actual Compensation Values Used:

<u>Rled</u> := 825

<u>Cz</u> := 330<u>n</u>

<u>Cp</u> := 22.7<u>n</u>

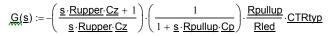

Finally, the chosen values are used in the TL431/optocoupler Transfer Function:

TL431/Optoisolator Transfer Function:

If Cpole less than 5x Cpcalc, use

Cpole in the Transfer Function

Bias Resistor:

<u>Rbias</u> =  $1.284 \times 10^3$

The two functions are multiplied together to achieve the overall loop gain:

$\underline{\text{Gtot431}(s)} := \underline{H}(\underline{s}) \cdot \underline{G}(\underline{s})$

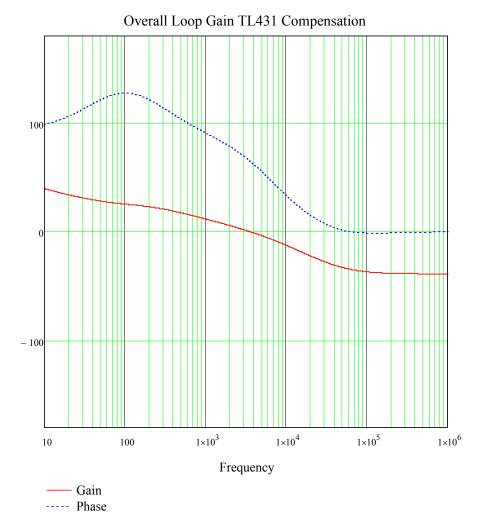

A Bode Plot of the overall loop gain is shown in Figure 6.

Using PD70101/PD70201 PD Front-End With Integrated PWM Controller ICs

COMPANY CONFIDENTIAL

#### Synchronous Gate Drive:

Copyright © 2010

Rev. 0.2, May, 2011

The PD70201 provides a dedicated output driver for a Synchronous FET. This output is available on the SG pin (pin 25). To adhere to the isolation requirements, the SG output is transformer coupled to the Synchronous FET. A coupling capacitor is required in series with the primary to reset the magnetizing inductance. The transformer will saturate without it. The LC tank circuit formed by the coupling capacitor and the transformer magnetizing inductance can generate oscillations during sudden changes in duty cycle. A damping resistor in series with the coupling capacitor should be used to damp oscillations. On the secondary side, a DC restoration and fast gate turn-off circuits are provided to keep the gate drive voltage constant over varying duty cycle, and to insure fast transistor turn off.

Referencing Figure 9, DC restoration is provided via Capacitor C20, and Diode D7. The fast turnoff circuit consists of R14, Q3 and D6. Resistor R11 limits the synchronous MOSFET's turn-on rate of rise, and is optional (can be used to limit EMI).

When selecting the components for the synchronous FET gate drive, first the transformer should be selected based on the maximum volt-microseconds of the SG pin drive output. Maximum volt-microseconds is calculated:

| <b>VCCmax</b> | := | 15 |

|---------------|----|----|

|               |    |    |

| <u>Dmin</u> = 0.323  | Duty Cycle at High Lin             | e                                               |

|----------------------|------------------------------------|-------------------------------------------------|

| <u>Vgdusecmax</u> := | ( <u>1 – Dmin</u> ).<br><u>Fsw</u> | $\underline{Vgdusecmax} = 5.081 \times 10^{-5}$ |

www.Microsemi.com

Because of the capacitor in series with the primary, the drive voltage is bipolar. The calculated maximum volt-microsecond value may divided by 2 for transformer selection due to the bipolar drive.

The magnetizing inductance will affect the transient response of the isolated drive signal. Generally a lower inductance will produce a faster response time. Our selected transformer has a magnetizing inductance of 296uH.

Once the transformer is selected, the two coupling capacitor values are calculated. The coupling capacitor values will determine the amount of ripple voltage seen at the gate of the synchronous FET; total gate ripple will be the sum of the individual capacitor ripple voltages.

To size the coupling capacitors, first determine the maximum ripple we will allow each capacitor to contribute to the overall gate ripple voltage. (~1% of the maximum gate drive voltage is chosen for our design). Next, factor in the values for synchronous FET gate charge, and the current flowing in the pull down resistor, R14:

| <u>Qg</u> := 31 <u>n</u>        | FDMS86322 Gate Charge                                     |

|---------------------------------|-----------------------------------------------------------|

| <u>Vdrv</u> := 12               | Nominal Gate Drive Voltage                                |

| $\Delta \underline{Vc1} := 0.1$ | Desired Ripple Across Primary Cap                         |

| Δ <u>Vc2</u> := 0.1             | Desired Ripple Across Secondary Cap                       |

| <u>Rgs</u> := 1 <u>k</u>        | Gate Resistor                                             |

| <u>D</u> := 0.95                | Off Time Duty Cycle (increased to account for transients) |

| <u>Lm</u> := 296 <u>u</u>       | Magnetizing Inductance                                    |